Micron 2017 Roadmap Detailed: 64-layer 3D NAND, GDDR6 Getting Closer, & CEO Retiring

by Billy Tallis on February 3, 2017 9:00 AM EST

At Micron's 2017 Analyst Conference yesterday in Scottsdale, Arizona, Micron executives provided updates on the status and future plans for all their major business units. While no new products were announced at this investor-focused event, their projections offer some insight about what's in store for the memory industry in 2017 and beyond. With both NAND flash and DRAM in short supply globally, Micron's projections of increasing production volume and decreasing cost per bit are welcome reassurance.

NAND Flash: 64-layer 3D NAND This Year, Additional Focus on Small Die Products

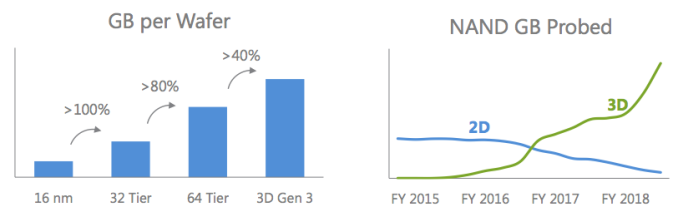

In 2016, Micron and Intel's joint venture became the second manufacturer to sell 3D NAND flash in volume. That 32-layer first generation 3D NAND has reached mature yields that are comparable to that of planar NAND processes, and since last fall 3D NAND has accounted for a growing majority of Micron's NAND output on a per-bit basis.

In 2017 Micron will be ramping up production of their 64-layer second generation 3D NAND, which is currently sampling. They promise "meaningful output" by the end of their fiscal year (December 2017). The 64-layer 3D NAND will increase the total GB per wafer by more than 80% and decrease the cost per bit of TLC by at least 30%.

With the second generation 3D NAND, Micron is shifting their strategy slightly by offering at least two different die sizes. We've previously heard about the 512Gb 64-layer 3D TLC part, but Micron will also be making a smaller 256Gb 3D TLC part. This die is planned to be the smallest 256Gb NAND flash die available from any vendor, at 59 mm^2 or 4.3Gb/mm^2. The smaller die is intended for the mobile market where the 512Gb part will be physically too large. Micron's market share for NAND in the mobile market has been quite low, in part because they tend toward making large, high-capacity chips. The new smaller part will give them a chance to go after a much larger share of the rapidly expanding mobile storage market. The smaller part may also see some use in the SSD market for the smallest models in each family, to avoid the pitfalls of having too few dies to stripe data accesses across.

Micron is not ready to share many specifics of their third generation 3D NAND flash, but they plan to begin small scale manufacturing in the second half of 2017. They are estimating that GB/wafer will improve by more than 40%, suggesting that they'll be moving to about 96 layers. They have not yet projected what cost per GB savings can be expected with the third generation 3D NAND.

Four bit per cell (QLC) NAND flash is also something Micron has worked on, but they do not yet have speficic plans for introducing it as a product. They are watching the demand quite closely and plan to be ready to introduce QLC NAND for certain cloud computing uses once the market is ready. (The very low write endurance of QLC NAND makes it necessary for software to be modified to minimize unnecessary writes, and QLC drives will generally not be suitable as drop-in replacement of 3D TLC NAND.)

DRAM: Sub-20nm This Year, GDDR6 Getting Closer

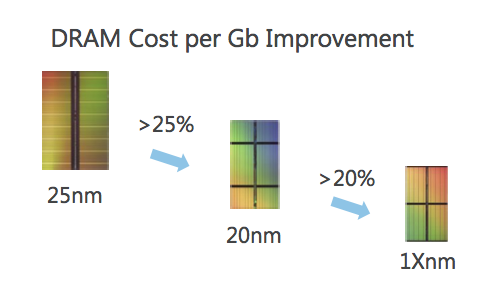

Last year, Micron ramped up production of their 20nm DRAM, and by the third quarter 20nm was a majority of Micron's DRAM output. In 2017, Micron will be ramping up and begin transitioning to their "1x nm" (16nm) node for DRAM, improving cost per GB by at least 20%. They plan to introduce 16nm GDDR5 later this year. Development is underway for both their 1Y nm and 1Z nm DRAM nodes, with initial manufacturing of 1Y nm DRAM expected to begin in the second half of 2017. Overall, they estimate the 1Y nm node is about a year behind the 1X nm node. GDDR5X volume is expected to grow significantly to satisfy bandwidth-hungry uses involving GPUs and networking, and around the end of this year or early next year Micron plans to introduce GDDR6 memory.

Other Memory Technologies: Still Quiet on 3D XPoint

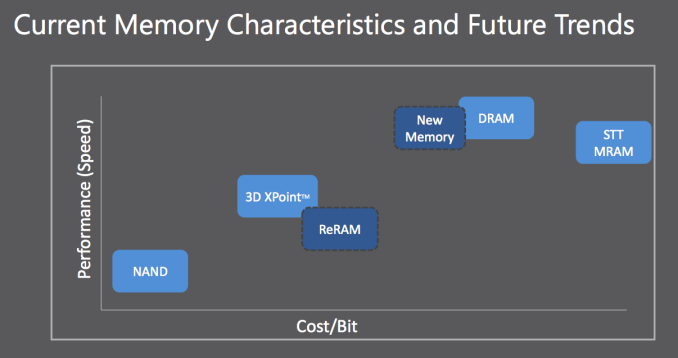

As usual, relatively little was said about 3D XPoint. Micron considers the memory to be "commercially ready" technology, with work underway on second and third generation 3D XPoint chips. The new generations will bring significant performance and density increases, but there are no numbers to back up those statements yet.

No specific products have been announced under their QuantX brand for 3D XPoint, but Micron plans to have some early market adoption of 3D XPoint by the end of the year. Even once 3D XPoint-based NVDIMMs are available, Micron is not concerned that 3D XPoint will significantly cannibalize their DRAM or NAND business.

Separate from 3D XPoint, Micron is working on at least one other new memory technology, as an in-house project instead of a collaboration with Intel. This new technology has not been named by Micron, but it will apparently allow for DRAM-like performance, which would be significantly higher than what 3D XPoint can deliver. This unspecified technology also has a clear potential for cost scaling, perhaps through increasing layering. The target it to be a bit slower and cheaper than DRAM, taking into account where DRAM technology is expected to be by the time this new memory comes to market. This is not at all an imminent revolution, and it could be a decade before it is mass produced and getting used in mainstream situations.

Trends: NAND Market Grows, EUV Slips Again

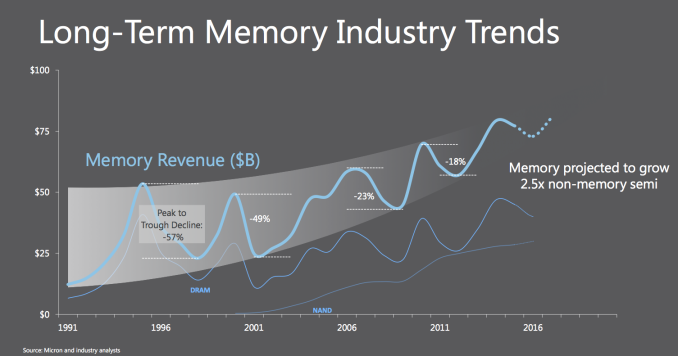

As for long-term trends, Micron sees the memory market as a whole becoming less volatile as DRAM's boom and bust cycles get less severe and NAND flash with its steadier growth accounts for an ever increasing share of the memory market. Weathering periods of oversupply and their associated price crashes is trying for memory manufacturers, and usually requires significant cuts to capital expenditures, which can delay the introduction of new technologies.

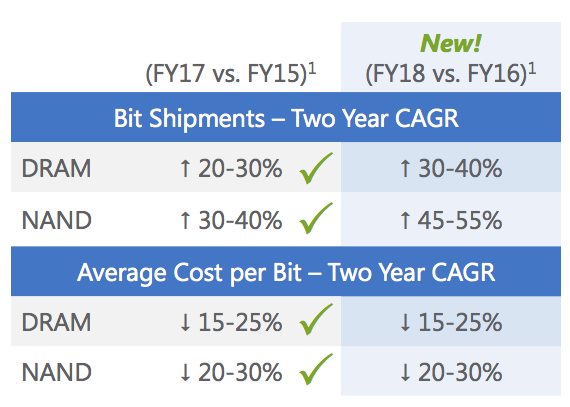

In spite of current shortages, Micron expects healthy growth in volume and decrease in cost per bit for both DRAM and NAND over the next few years. NAND flash sales are expected to grow faster than DRAM, so while DRAM is currently a larger part of Micron's business than NAND flash, that may change in a few years. Micron expects the memory market as a whole to grow at about 2.5 times the growth rate of the rest of the semiconductor industry.

In general, Micron is not looking to become significantly more vertically integrated. In particular, they do not want to become a competitor to their valuable DRAM customers. However, Micron is pursuing innovations in packaging, and they want to significantly expand their market share for what they call heterogeneous multi-chip packaging (xMCP): putting DRAM, NAND and logic in one package, such as for mobile devices or BGA SSDs.

Meanwhile it will surprise absolutely nobody to hear that Micron's deployment of extreme ultraviolet (EUV) lithography has experienced a setback. Last spring Micron reported that they planned to have their first EUV tool installed in their research fab by the end of the year. The equipment is in place but not online yet, so Micron does not yet have any preliminary results to report. Micron says nothing on their current roadmaps requires EUV, so at this point it is just a potential for cheaper or more efficient manufacturing, not a looming roadblock.

Finally, after three decades with Micron and having spent the past five years as its CEO, Mark Durcan has announced his intention to retire as soon as the board of directors can hire a successor. Durcan had previously announced plans to retire in 2012 while serving as the company's president, but the death of then-CEO Steve Appleton prompted Durcan to postpone his retirement indefinitely to serve as Micron's CEO. A new CEO could be found in a matter of weeks or the search may take months; either way, Durcan plans to stick around to ensure a smooth transition.

Source: Micron

44 Comments

View All Comments

Yojimbo - Friday, February 3, 2017 - link

Seems not. It sounds more and more like TSV memory will remain pretty expensive. Besides, I don't think graphics cards need that sort of bandwidth yet. GPU compute cards do, but not graphics cards. So for most graphics cards it ends up adding a whole lot of cost for some energy savings. Not worth it.lilmoe - Friday, February 3, 2017 - link

Cost...vladx - Friday, February 3, 2017 - link

^Thiswumpus - Saturday, February 4, 2017 - link

Cost and expansion. Ideally I'd like HBM2 (supposedly lower cost than HBM) and DDR5/6 made out of 3dxpoint or other stuff that is cheaper than DRAM.But don't be surprised if phones stick to DDR[n] as well even though HBM should allow less power to be consumed (flagship models might loudly use HBM).

WulfTheSaxon - Friday, February 3, 2017 - link

“In particular, they do not want to become a competitor to their valuable DRAM customers”? I think I see the slide where that comes from: “Partner as opposed to competitor toour customers” as a bullet-point under "Why Micron Wins". But did they forget that they sell enterprise and consumer SSDs and RAM, memory cards, thumb drives, and more both directly and through their Crucial and Lexar subsidiaries? All I can think they’re referring to is their spinning off MicronPC back in 2001, which seems like an odd thing to mention. >.<

Guspaz - Friday, February 3, 2017 - link

I'm starting to think that 3D XPoint is going to be too slow to replace DRAM, and too expensive to replace NAND, even as a write cache (since SLC is already used as a high-endurance write cache for modern consumer SSDs). Unless the cost comes down by a huge margin, it's going to end up as a niche product that never makes it out of enterprise use where there's a need for absurdly high IOPS.MrSpadge - Friday, February 3, 2017 - link

Of course it won't replace DRAM in almost all usage scenarios. It's got a few orders of magnitude higher write endurance than NAND, which means it would still wear out pretty quickly if used as regular main memory.wumpus - Saturday, February 4, 2017 - link

It should be able to replace *some* DRAM, but not all. It looks like its best chance is to try to shove itself into the memory hierarchy. Something like:onchip cache->HBM dram (on interposer)->3dxpoint (DDR[n]-like bus)->bulk flash (pci-e/m.2 bus)

The point about the "bulk flash" is that the 3dxpoint should take up most of the buffer duties and act like a cache for the flash drives. This should make SSDs more of a commodity. I'm guessing the biggest threat to 3dxpoint is 3dflash's* ability to get some deep wells to act more like SLC (especially in endurance) and act as it's own buffer circuit (this is the DRAM 3dxpoint "should" be replacing).

* I'd think this works in 2d, but can't say I've heard of it being done.

fanofanand - Monday, February 6, 2017 - link

Unless it is part of the package (whether that's on-die or within the chipset) then it is anti-consumer to try to wedge yet another product in the memory hierarchy. We need LESS points of failure, not more.martinw - Friday, February 3, 2017 - link

" Micron sees the memory market as a whole becoming less volatile"I see what you did there...