Toshiba's 768Gb 3D QLC NAND Flash Memory: Matching TLC at 1000 P/E Cycles?

by Anton Shilov on July 3, 2017 2:30 PM EST

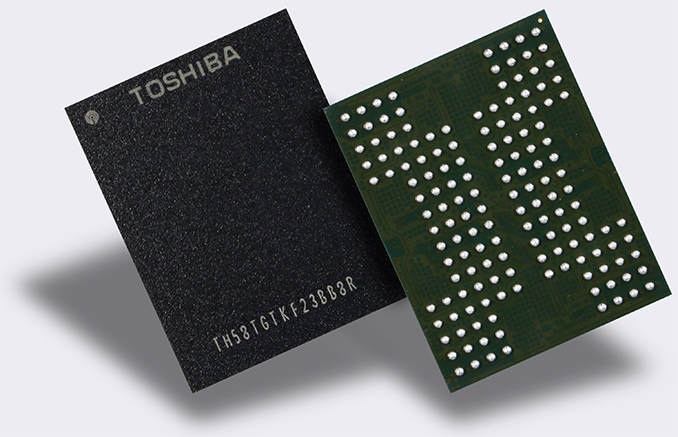

Toshiba last week announced its first 3D NAND flash memory chips featuring QLC (quadruple level cell) BiCS architecture. The new components feature 64 layers and developers of SSDs and SSD controller have already received samples of the devices, which Toshiba plans to use for various types of storage solutions.

Toshiba’s first 3D QLC NAND chips feature 768 Gb (96 GB) capacity and uses 64 layers, just like the company’s BICS3 chips with 256 Gb and 512 Gb capacities launched in 2016 and 2017. Toshiba does not share further details about its 3D QLC NAND IC (integrated circuit), such as page size, the number of planes as well as interface data transfer rate, but expect the latter to be high enough to build competitive SSDs in late 2018 to early 2019 (that’s our assumption). Speaking of applications that Toshiba expects to use its 3D QLC NAND ICs, the maker of flash memory mentions enterprise and consumer SSDs, tablets and memory cards.

Endurance++

Besides intention to produce 768 Gb 3D QLC NAND flash for the aforementioned devices, the most interesting part of Toshiba’s announcement is endurance specification for the upcoming components. According to the company, its 3D QLC NAND is targeted for ~1000 program/erase cycles, which is close to TLC NAND flash. This is considerably higher than the amount of P/E cycles (100 – 150) expected for QLC by the industry over the years. At first thought, it comes across a typo - didn't they mean 100?. But the email we received was quite clear:

- What’s the number of P/E cycles supported by Toshiba’s QLC NAND?

- QLC P/E is targeted for 1K cycles.

It is unclear how Toshiba managed to increase the endurance of its 3D QLC NAND by an order of magnitude versus initially predicted. What we do know is that signal processing is more challenging with QLC than it is with TLC, as each cell needs to accurately determine sixteen different voltage profiles (up from 2 in SLC, 4 in MLC, and 8 in TLC).

The easiest way to handle this would be to increase the cell size: by having more electrons per logic level, it is easier to maintain the data and also read from it / write to it. However, the industry is also in a density race, where bits per mm^2 is an issue. Also, to deal with read errors from QLC memory, controllers with very advanced ECC capabilities have to be used for QLC-based SSDs. Toshiba has its own QSBC (Quadruple Swing-By Codes) error correction technique, which it claims to be superior to LDPC (low-density parity-check) that is widely used today for TLC-powered drives. However, there are many LDPC implementations and it is unknown which of them Toshiba used for comparison against its QSBC. Moreover, there are more ECC methods that are often discussed at various industrial events (such as FMS), so Toshiba could be using any or none of them. The only thing that the company tells about its ECC now is that it is stronger than 120 bits/1 KB used today for TLC. In any case, if Toshiba’s statement about 1000 P/E cycles for QLC is correct, it means that that the company knows how to solve both endurance and signal processing challenges.

The main advantage of QLC NAND is increased storage density when compared to TLC and MLC, assuming the same die size. As was perhaps expected, die size numbers were not provided. However, last year Toshiba and Facebook talked about a case study QLC-powered SSD with 100 TB of capacity for WORM (write once read many) applications and it looks like large-capacity custom drives and memory cards will be the first to use QLC for cold storage. P/E cycles and re-write endurance isn't a concern for WORM at this stage.

Toshiba has begun to sample its 3D QLC NAND memory devices earlier this month to various parties to enable development of SSDs and SSD controllers. Taking into account development and qualification time, Toshiba plans to mass produce its BiCS3 768 Gb 3D QLC NAND chips around the same time it starts to make its the next generation BiCS4 ICs. The latter is set to hit mass production in 2018, but the exact timeframe is yet to be determined.

Related Reading:

- Western Digital Announce BiCS4 3D NAND: 96 Layers, TLC & QLC, Up to 1 Tb per Chip

- Toshiba Selects Japan-U.S. Consortium As Preferred Buyer For Memory Business

- Toshiba Introduces XG5 Client NVMe SSD

- Western Digital Ships Client SSDs Based on 512 Gb 3D TLC NAND Chips

- Toshiba Samples 64-Layer 512 Gb BiCS 3D NAND, Announces 1 TB BGA SSD

- Toshiba Finalizes Plans for New 3D NAND Fab: Coming Online in 2019

Source: Toshiba

36 Comments

View All Comments

mkozakewich - Wednesday, July 5, 2017 - link

Keep in mind, four bits is only 33% more than three bits. They immediately jumped to the idea of 100TB drives, but it looks like their upcoming QLC chips would support about 4TB. (Or 8 TB, maybe.)Alexvrb - Wednesday, July 5, 2017 - link

I have a 3TB HDD for secondary storage. A 4TB would be plenty. :D Pricing, of course, is key. I don't anticipate being able to go all-solid-state for at least a couple of years.Lolimaster - Wednesday, July 5, 2017 - link

For media you don't SSD at all, HDD's are plenty fast and responsive for it. Another thing is having a huge collection of images where you want to use the thumbnails often.beginner99 - Wednesday, July 5, 2017 - link

And the race to bottom just reached a new low. Won't be far till be reach JMicron level of bad.nandnandnand - Wednesday, July 5, 2017 - link

This article has some serious grammar problems. Maybe 4 mistakes in the first two paragraphs.Gasaraki88 - Wednesday, July 5, 2017 - link

I'm not trusting QLC with my data. Some TLC are bad enough. Maybe for WORM storage but no way for daily use. They can lie about the 1000 P/E cycles all they want.BurntMyBacon - Wednesday, July 5, 2017 - link

3D-QLC getting 1000 P/E cycles is not as improbable as it seems. Samsung's move to 3D-NAND brought an odd situation where the MLC based 840PRO had less endurance than the TLC based 850EVO. Intel / Micron didn't get this benefit as they chose to use floating gates instead of charge traps in their architecture. Samsung, SK Hynix, and Toshiba all use charge trap. If I recall correctly, the 1000 P/E cycles metric is where planer NAND ended up. It is conceivable that Toshiba was able to make a 3D-QLC NAND with equal endurance to its planer TLC predecessor similar to how Samsung achieved a 3D-TLC with greater endurance than its planer MLC predecessor.However, I don't recall ever hearing 1000 P/E cycles used to describe the endurance of a 3D-TLC (charge-trap) NAND chip. An appropriate comparison point would be Toshiba's 3D-TLC vs Toshiba's 3D-QLC. That would help us to understand the true trade-offs made when moving to QLC.

Glaring_Mistake - Wednesday, July 5, 2017 - link

I can see that 3D QLC NAND could get to 1000 P/E cycles but that the 850 EVO has a higher endurance than the 840 Pro is just not accurate - the 850 EVO is rated at 2000 P/E and the 840 Pro at 3000 P/E.850 EVO may have a higher TBW but that is not the same as endurance.

Nor are they likely to have established TBW in the same way since the 840 Pro had a TBW of 72TB if it was used as an enterprise-class drive.

Endurance for planar TLC NAND varies quite a bit too, for example the Kingston UV400 is rated at 400-500 P/E while the Plextor M7V is rated at 2000 P/E, despite using the same NAND and controller!

So it is not like 1000 P/E is set in stone for planar TLC NAND.

Finally the 960 EVO was found by Nordichardware to be rated at around 1200 P/E despite using 3D TLC NAND with a Charge Trap.

BurntMyBacon - Monday, July 17, 2017 - link

@Glaring_MistakeNever saw an official endurance rating for the 850 EVO, so I was extrapolating from the TBW (note I didn't say P/E cycles here where it did later). The 840 Pro is a consumer drive, so I had no reason to believe they would be rated differently. I did however come across this article when looking up your 2000 P/E number suggesting that the 850 EVO does in fact have less endurance than the 840PRO. Good catch there.

@Glaring_Mistake: "Endurance for planar TLC NAND varies quite a bit too, for example the Kingston UV400 is rated at 400-500 P/E while the Plextor M7V is rated at 2000 P/E, despite using the same NAND and controller! So it is not like 1000 P/E is set in stone for planar TLC NAND."

Perhaps, I should have specified that I was talking about Samsung planer TLC for that 1000 P/E cycles. I thought it was self evident as my comparison was between Samsung flash, but in hindsight, I did mention other companies as examples of who uses charge trap and floating gate.

I agree that TLC NAND varies, which is why I stuck with the same manufacturer and as close to the same controller as possible. Design of the cells, size of the cells, process, and even software considerations like error correction method can all contribute to the endurance of the NAND. This is why it is impractical to compare endurance of flash from different manufacturers using different controllers and running different firmware. The Kingston UV400 and Plextor M7V is a perfect example of how NAND with the same NAND and controller with identical physical endurance can get wildly different ratings depending on the firmware (different error correction methods). This does little to alleviate my fears regarding QLC and even gives me pause regarding TLC.

@Glaring_Mistake: "Finally the 960 EVO was found by Nordichardware to be rated at around 1200 P/E despite using 3D TLC NAND with a Charge Trap."

I'm guessing this is another unofficial rating, but it seems logical. I would expect the 960 EVO with Charge Trap base 3D TLC NAND NAND built on a smaller process to have less endurance than 850 EVO with Charge Trap base 3D TLC NAND built on a larger process. That's before your consider that you have a couple of generations difference in controller and firmware that makes it even harder to compare. I short, I'm not sure what you are trying to say here.

BurntMyBacon - Wednesday, July 5, 2017 - link

Unfortunately, despite all the data that suggests TLC has plenty of endurance for consumers, I can't bring myself to put a TLC drive in my personal system. I have not problem putting one in a client system after making sure they are fully aware of the trade-offs, though. However, I can't in good conscience recommend a QLC drive even with the 1000 P/E cycle rating as I know how they are getting there.It's like comparing a higher quality recording to a recording with pops, artifacts, and distortion. In this case, they would call them equal because the listener on the junk recording was more adept and was able to understand the same number of words as the listener on the higher quality recording.

Just because you have better error correction, doesn't mean you haven't exceeded to limits of the NAND and caused errors. The more errors you have to contend with, the more you are playing a probability game of can you correct the errors and still retrieve your data, or will you hit a particularly bad sequence of errors that is outside of your error correction algorithm's ability to correct.