Hot Chips 31 Keynote Day 2: Dr. Phillip Wong, VP Research at TSMC (1:45pm PT)

by Dr. Ian Cutress on August 20, 2019 4:00 PM EST

04:41PM EDT - The keynote for the second day is from TSMC, with Dr. Phillip Wong taking the stage to talk about the latest developments in TSMC's research and portfolio. The talk starts at 1:45pm PT / 4:45pm ET.

04:42PM EDT - Everyone is coming back from lunch and we'll start in a few minutes

04:43PM EDT - This final session will have talks on TSMC, Gen-Z, TeraPHY, a break, then Intel Lakefield, Xeon Jintide, and Hololens 2.0 Silicon

04:47PM EDT - Dr. Philip Wong, VP of Corporate Research, in charge of new process technologies

04:48PM EDT - Spent 16 years at IBM, over 600 papers

04:48PM EDT - A talk about the technology, not about the products

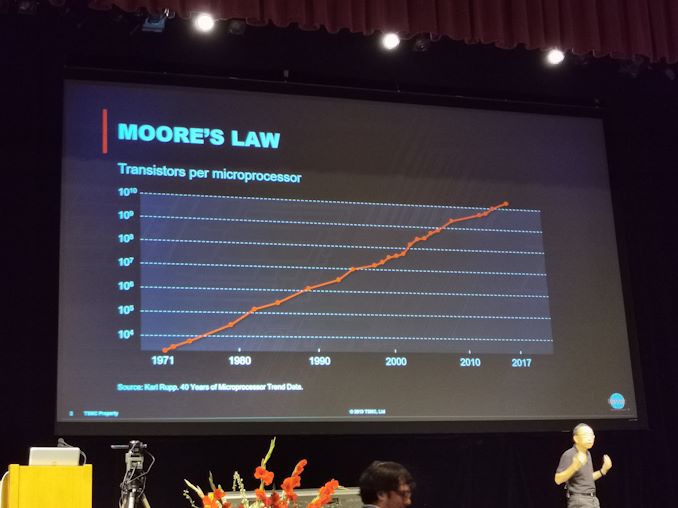

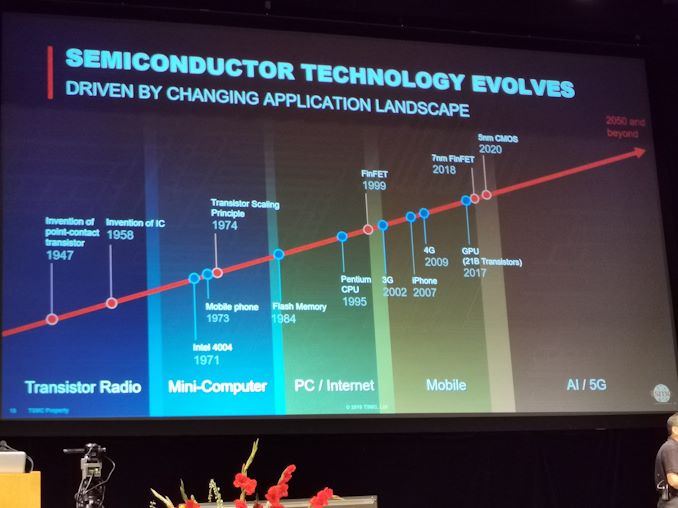

04:49PM EDT - Moore's Law, from 1971 to 2017

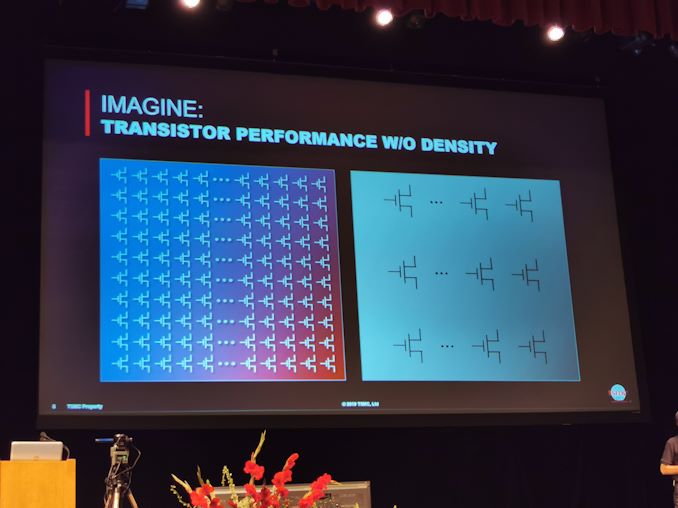

04:49PM EDT - Moore's Law is about density

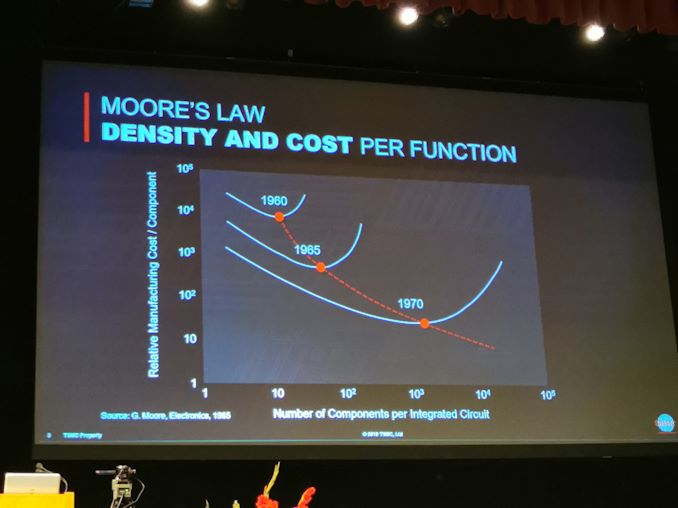

04:49PM EDT - Moore's original paper

04:50PM EDT - Density matters because it's the primary driving force for high performance logic

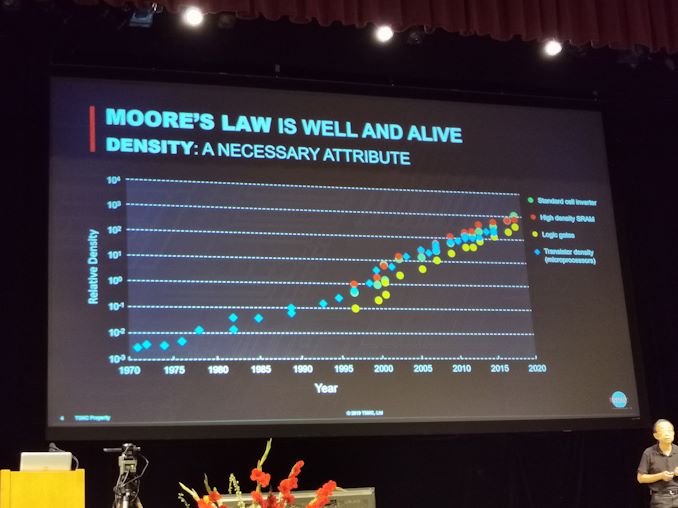

04:50PM EDT - Density is still on the same log trajectory on a log linear plot

04:50PM EDT - Even to 2020

04:51PM EDT - Moore's Law is a live and well. Who said it was dead? Density is increasing, and will increase

04:51PM EDT - New attributes are being requested, like clock speed or efficiency, which Moore's Law doesn't care about

04:52PM EDT - Density is still king - memory, cores, accelerators

04:52PM EDT - Wire delay with the best transistors means nothing without density

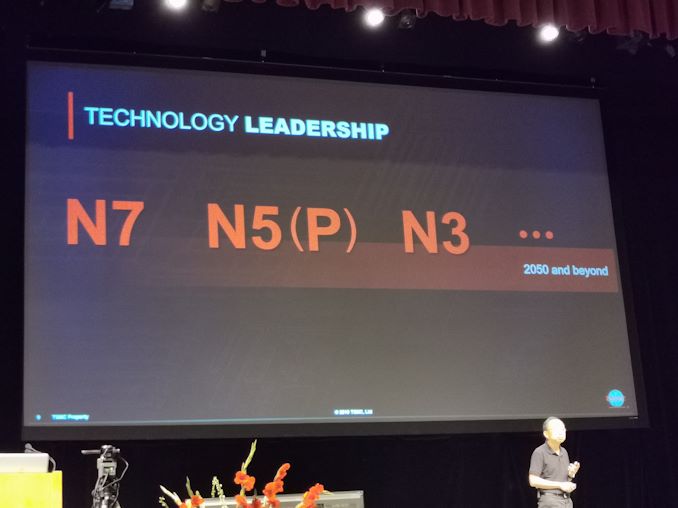

04:52PM EDT - N7

04:53PM EDT - Worlds First 7nm

04:53PM EDT - N5(P) is next, using EUV extensively, already in risk production

04:53PM EDT - Then N3

04:54PM EDT - The number used to mean something about the features. Now they are just numbers, like car model numbers

04:54PM EDT - Do not confuse the name of the node with the tech actually offered

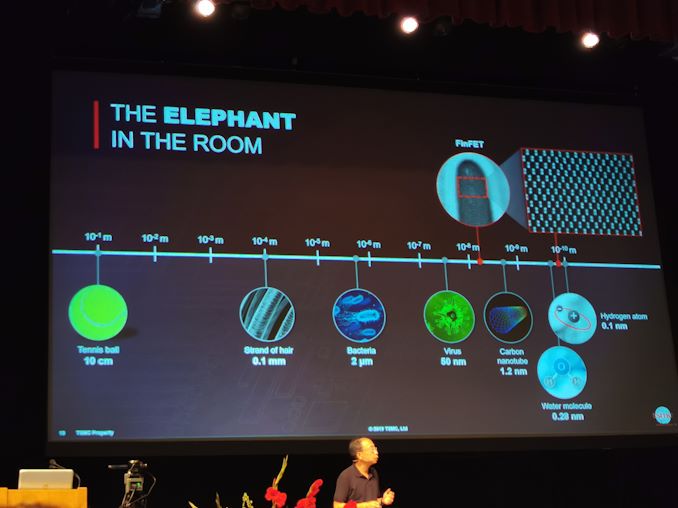

04:55PM EDT - FinFET fins, atoms are easily countable now

04:55PM EDT - 2D dimensional scaling is slowly becoming limited due to atom count

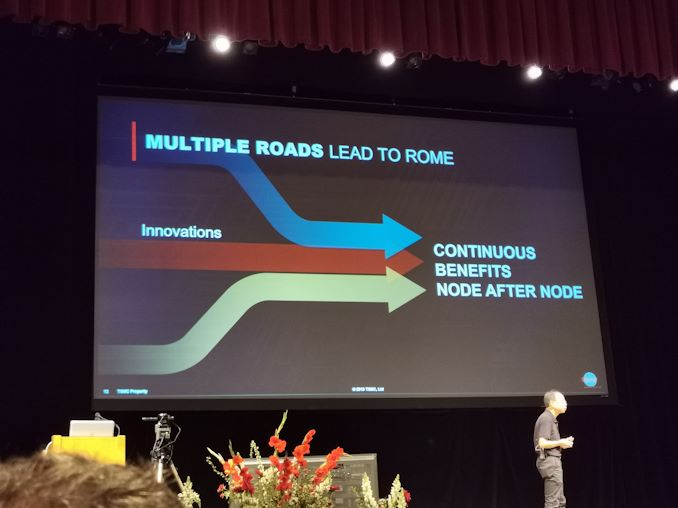

04:56PM EDT - But finfet size is not the only knob that can be tuned to confirm to Moore's Law

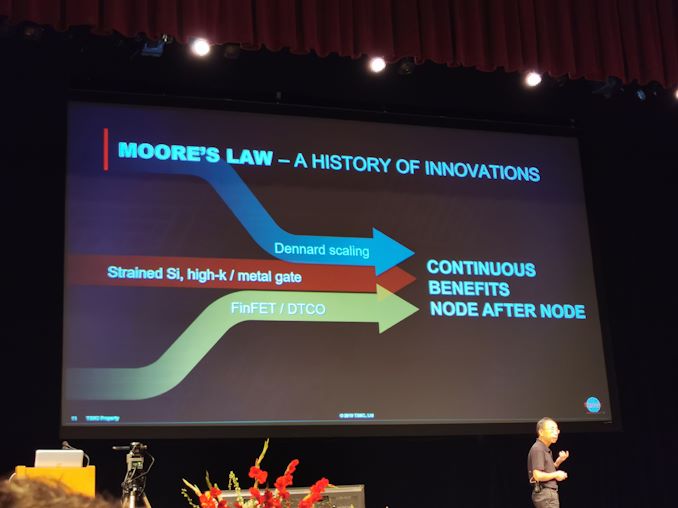

04:56PM EDT - Strained Si, High-K, 2D to 3D FinFET etc

04:56PM EDT - Design co-optimization

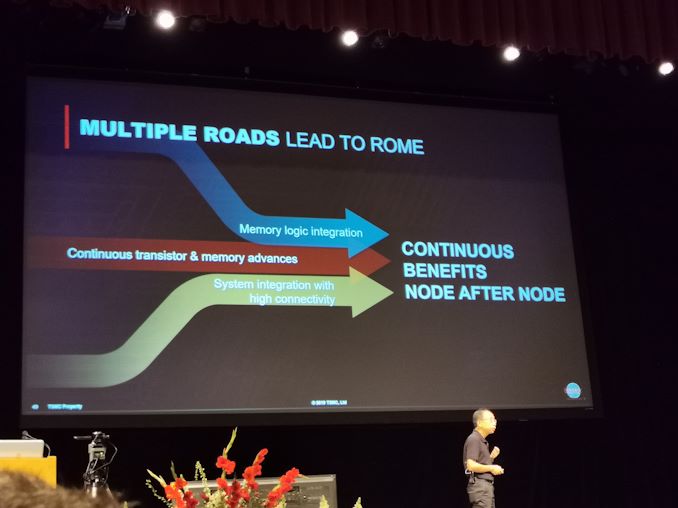

04:57PM EDT - Continuous benefits node after node

04:57PM EDT - 'All roads lead to Rome'

04:57PM EDT - Is that an AMD reference?

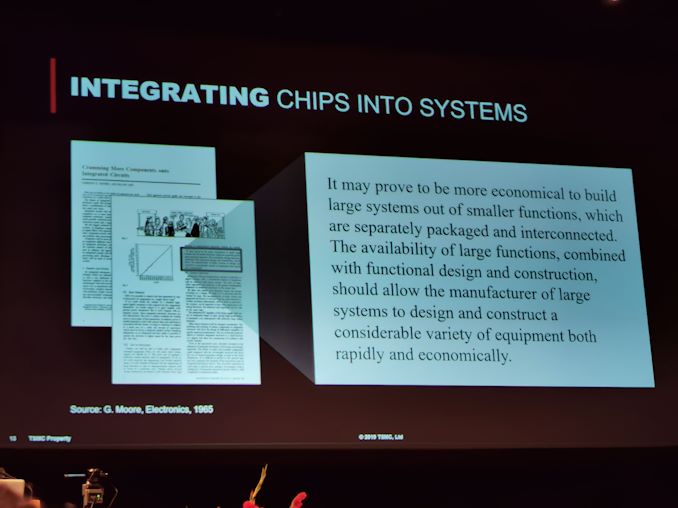

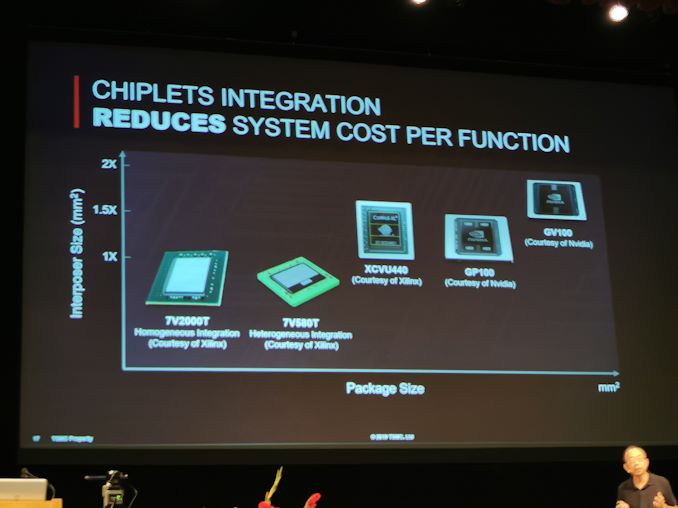

04:57PM EDT - In Moore's Paper, Page 3 predicted chiplets

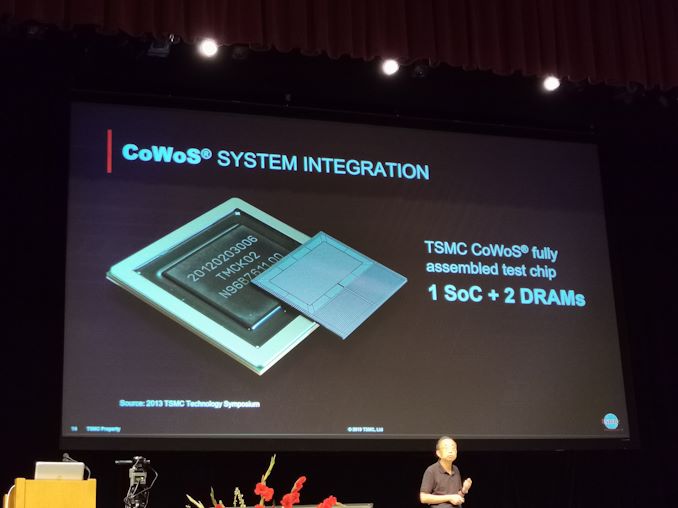

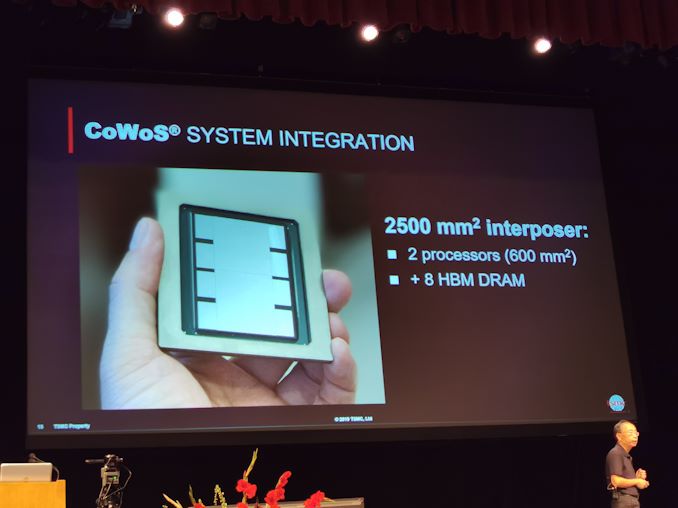

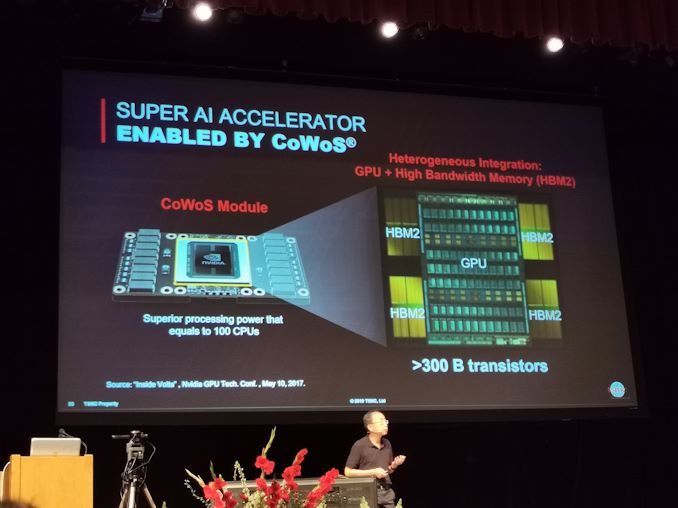

04:58PM EDT - At TSMC, CoWoS

04:58PM EDT - Chip on Wafer of Substrate

04:59PM EDT - Much of the technology is driven my top down system innovations, not bottom up

05:00PM EDT - Moving to an AI/5G era

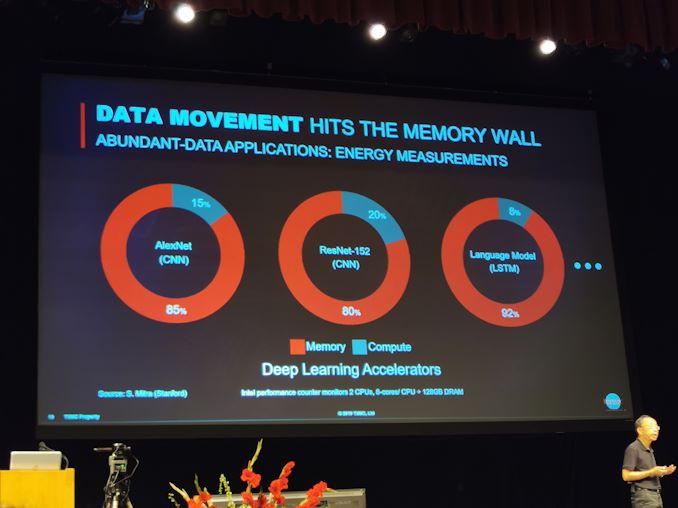

05:01PM EDT - Data movement means we have hit a memory wall

05:01PM EDT - Today, memory access controls the energy efficiency

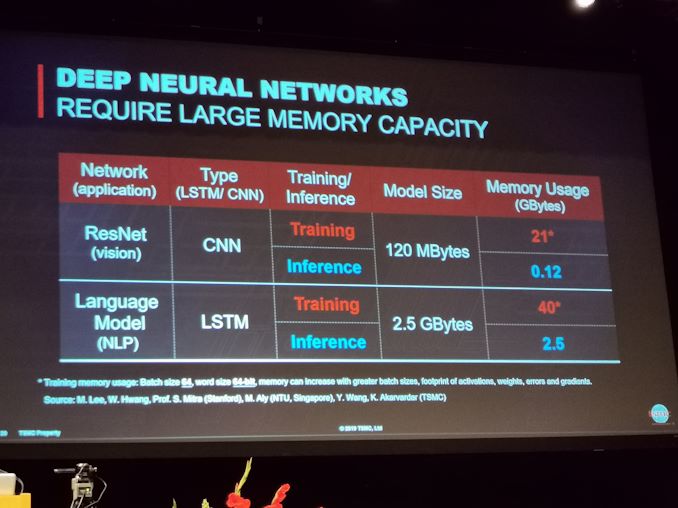

05:02PM EDT - Deep Neural Networks require large memory capacity

05:02PM EDT - This is today's problem. Tomorrows problem will be more demanding on memory

05:03PM EDT - Need more SRAM on chip

05:03PM EDT - There will never be enough SRAM on the chip, that is clear

05:03PM EDT - How can we put lots of memory on chip

05:04PM EDT - What kinds of memory is important

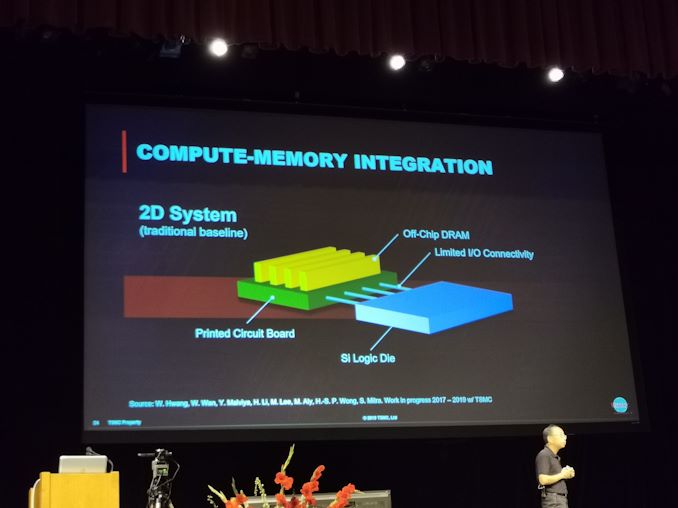

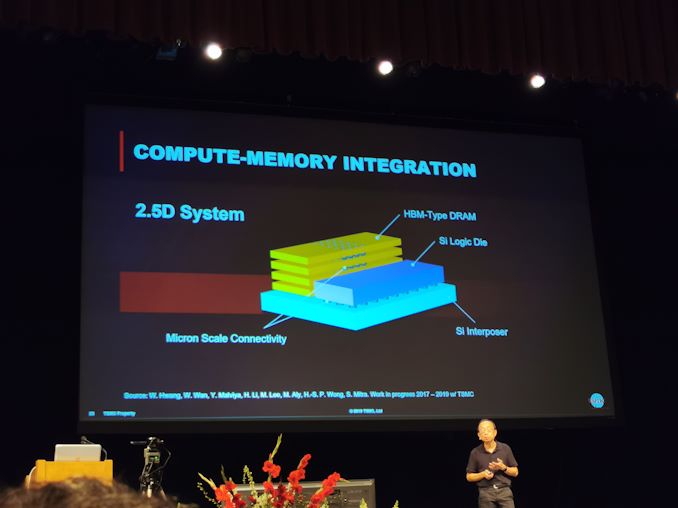

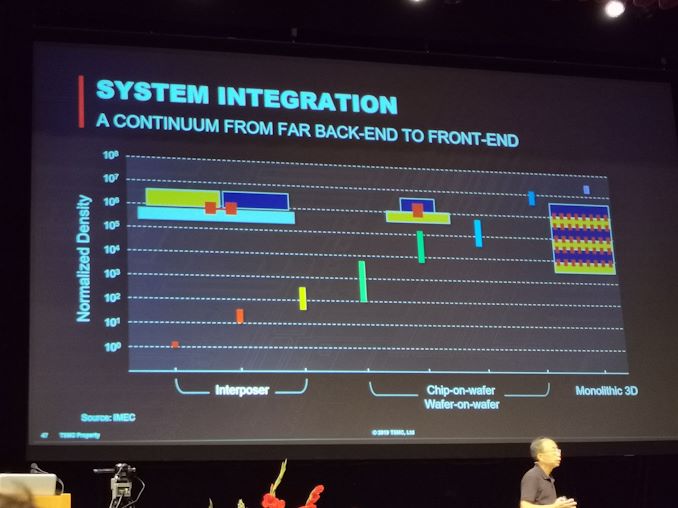

05:04PM EDT - A variety of systems today - 2D and 2.5D

05:05PM EDT - 2.5D uses TSVs

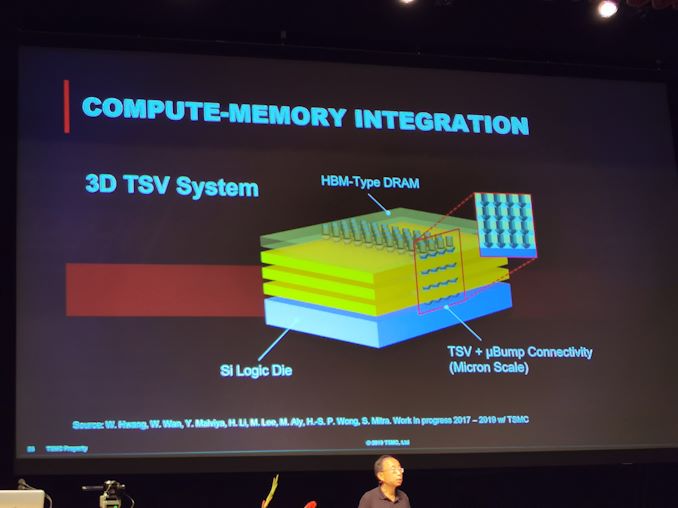

05:05PM EDT - One step further is 3D

05:06PM EDT - Connectivity has improved over 2.5D and 2D

05:06PM EDT - Connectivity on the order of microns is even not enough

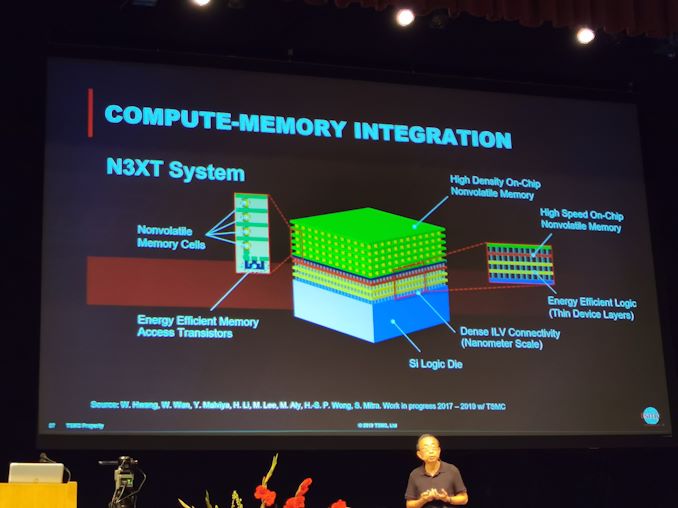

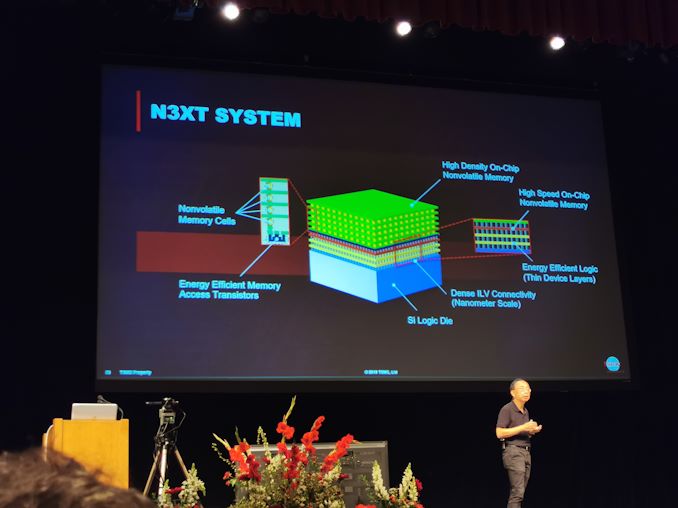

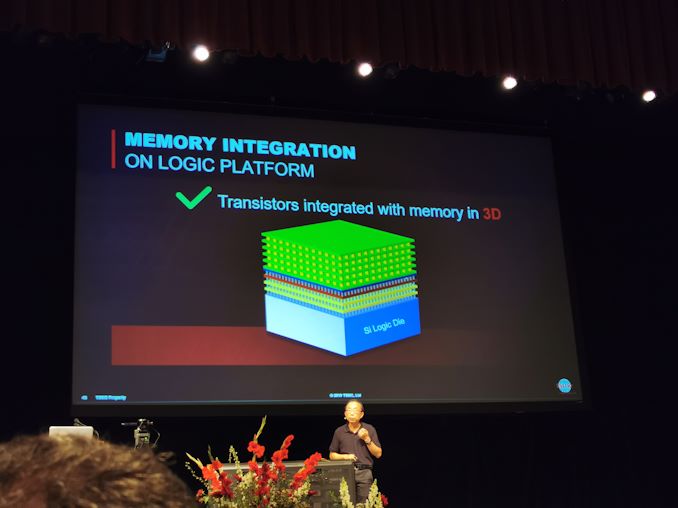

05:07PM EDT - Beyond 3D is combining logic and memory and integrating them

05:07PM EDT - Multiple layers of memory and logic

05:07PM EDT - Dense TSVs, on order of nm

05:07PM EDT - It's a 'N3XT' level system

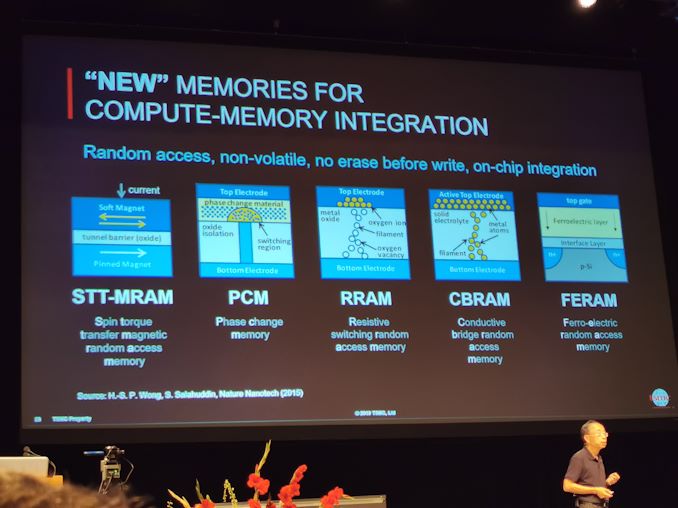

05:08PM EDT - Lots of New memories to solve this issue

05:08PM EDT - STT-MRAM, PCM, RRAM, CBRAM, FERAM

05:09PM EDT - Many of them are already in products

05:09PM EDT - 22nm MRAM eg

05:09PM EDT - on-chip integration is important

05:11PM EDT - have to be done at low temperature ofc

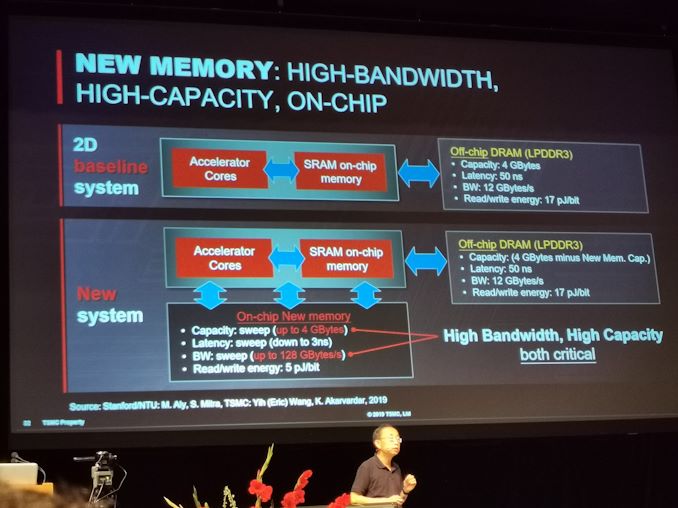

05:11PM EDT - New memory has to be high bandwdith, high capacity, and on chip

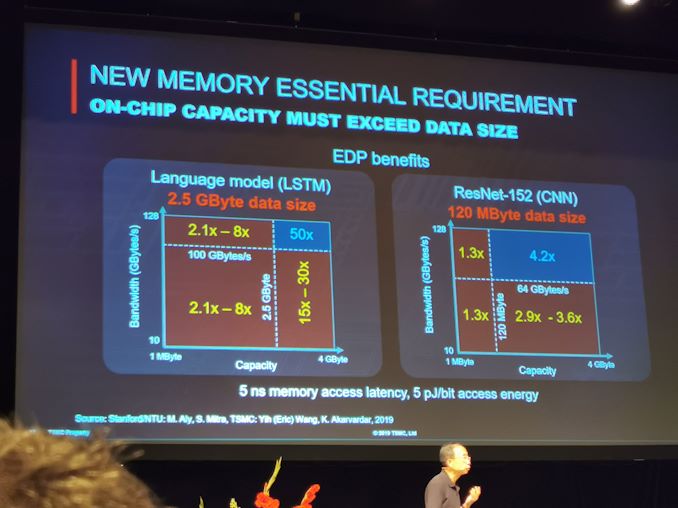

05:13PM EDT - On-chip capacity must exceed data size

05:13PM EDT - This graphs show the potential speedups

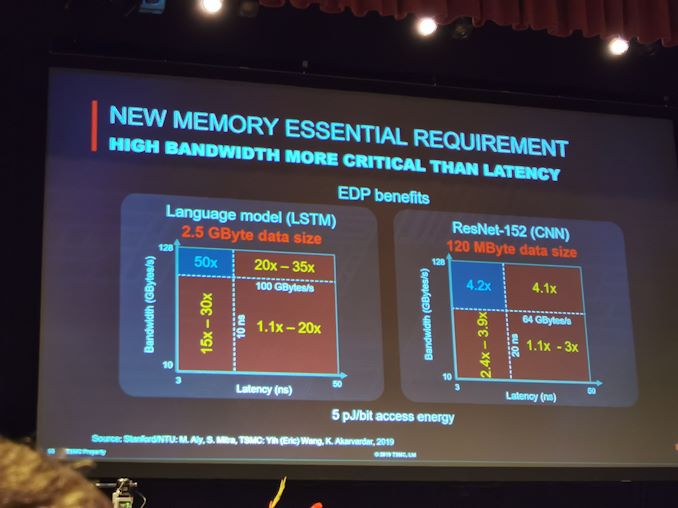

05:14PM EDT - More bandwidth is often more critical than latency

05:15PM EDT - So new memory has to have high-bandwidth and high-capacity for model training

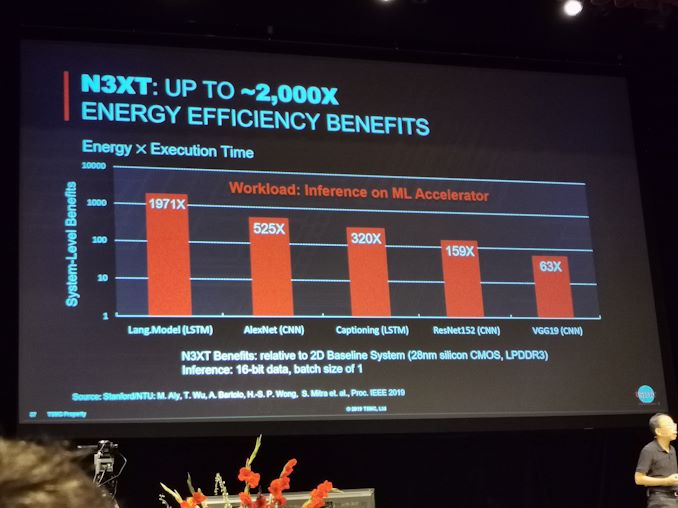

05:16PM EDT - Can do research to see benefits up to 2000x with enough memory on chip with high enough bandwidth with tight logic-memory integration

05:17PM EDT - A lot of memory requires a lot of logic that has to be interleaved with each other

05:17PM EDT - Not quite possible with today's technology

05:17PM EDT - Difficult to built high perf transistors on upper layers because it requires >1000C at manufacturing, which degrades memory layers

05:18PM EDT - Need thin device layers and low fabrication temperature to build this ideal system

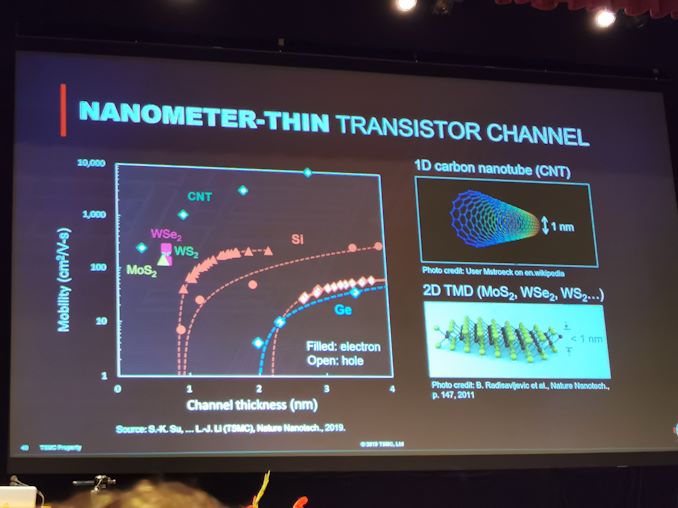

05:19PM EDT - Transistor technology has had a lot of advancements recently

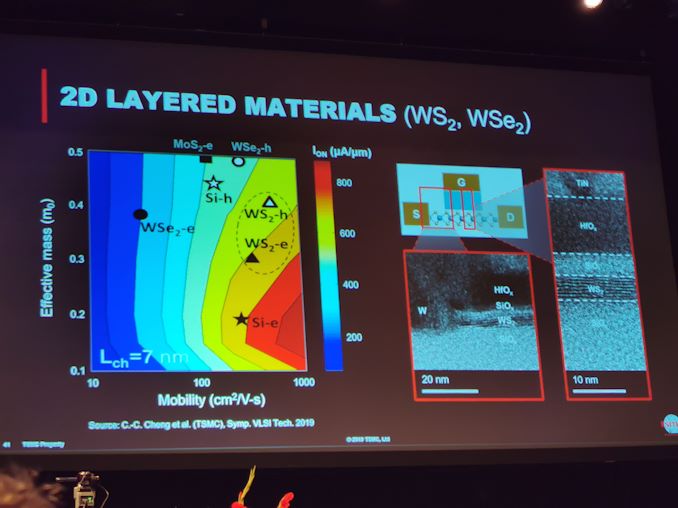

05:20PM EDT - 2D layered materials, like 2D TMD Transition Metal Designs (MoS2, WSe2, WS2)

05:20PM EDT - or 1D materials, like Carbon Nanotubes

05:20PM EDT - These materials have high carrier mobility, and are very thin

05:21PM EDT - Making channel thickness smaller, but keeping mobility high

05:21PM EDT - THis is an important slide

05:22PM EDT - There are almost 2000 TMD options, need to select the best ones

05:22PM EDT - Also need to have reasonable effective mass

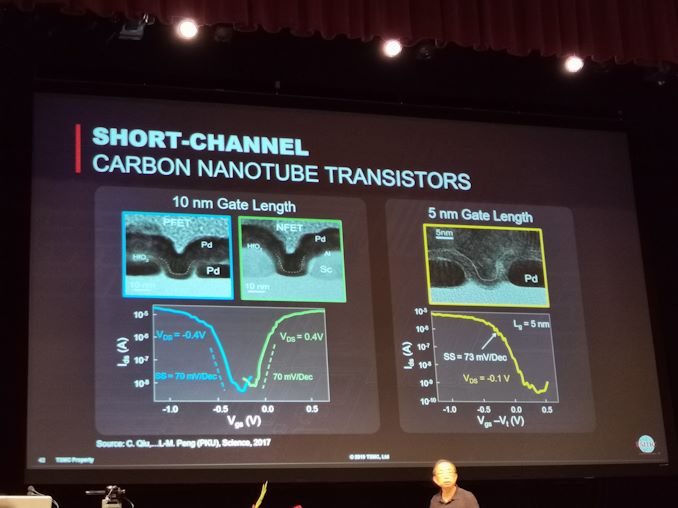

05:23PM EDT - Now 1D

05:23PM EDT - CNTs have been around 20 years

05:24PM EDT - 20+

05:24PM EDT - CNTs have excellent characteristics for transistors

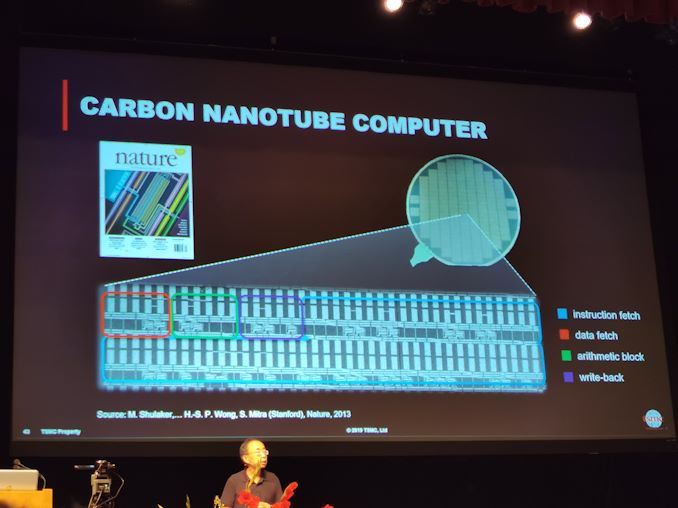

05:24PM EDT - Have showed complete computer running in CNT with no silicon

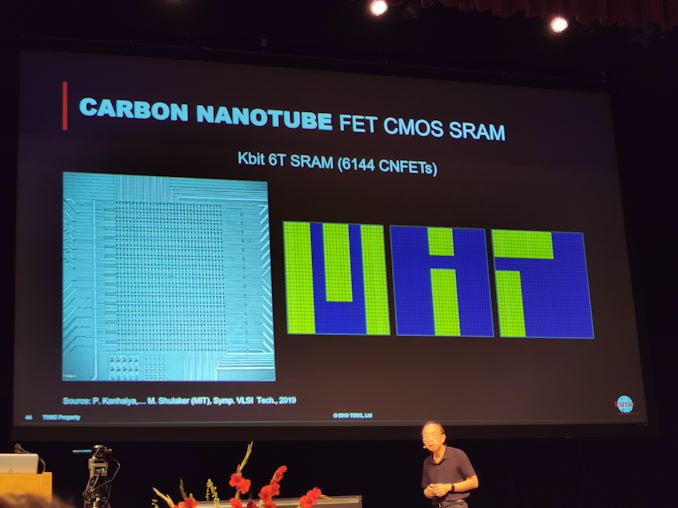

05:25PM EDT - Also shown SRAM 6T built out of CNTs

05:25PM EDT - 6144 CNFETs

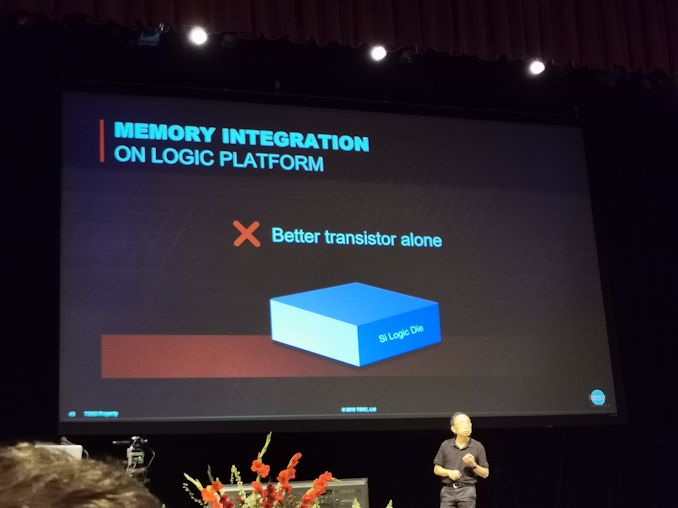

05:26PM EDT - Overall, you don't only just need better transistors, you need better integration with memory

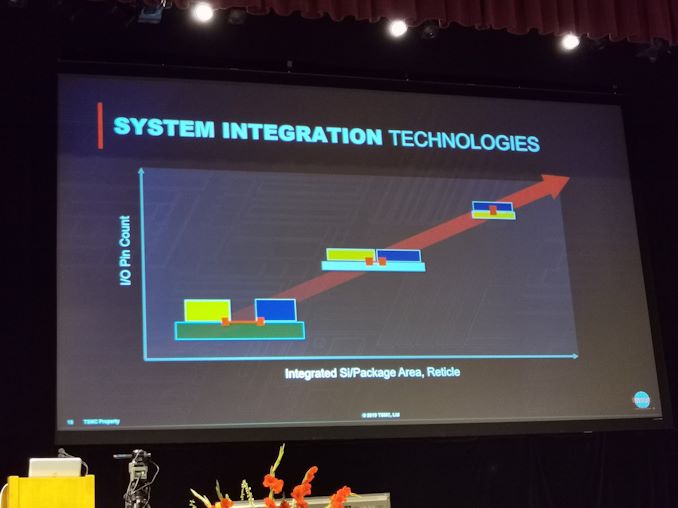

05:27PM EDT - Use a variety of system integration techniques. It's a continuum

05:28PM EDT - Advanced technology is a key differentiator

05:30PM EDT - A call to action: early engagement between system engineers and technology development

05:30PM EDT - Need a much closer interaction between device technology and requirements

05:31PM EDT - Academia needs to work closely with industry research, moreso today than ever before

05:31PM EDT - Q&A time

05:32PM EDT - Q: Variability in CNT SRAMs? A: Yes in the paper. Today we are limited by university fab capabilities. Variability is due to the uncontrollability in university fabs. Variability would not be very different from commercial silicon but more refined

05:36PM EDT - Q: Analog memory computing may not have a future? A: I have no particular ocmment about analog computing, but device density is important. One way is 3D integration of logic and memory. Density is what drives Moore's Law. We need to provide device density and connectivity density and that will remain important.

05:39PM EDT - Q: How to software companies work with TSMC in the future? A: Development of logic and memroy has been rather separate in the past, so memory technology and fab of memory needs to recombine. This is going to be a compute issue that software will have to be able to use. Make it worth while, like 22nm MRAM, or 22 RRAM. It takes early engagement between research with a system view and engage with the tech side, together we can figure out what is the right technology mix

05:39PM EDT - That's a wrap. Next talk is Gen-Z

11 Comments

View All Comments

blogvile - Wednesday, February 12, 2020 - link

Nice Blog. Thanks dear for sharing this interesting information with us and put your thoughts in this blog. https://www.pattachitta.com and https://www.blogvile.com/