Arm & TSMC Showcase 7nm Chiplet, Eight A72 at 4GHz on CoWoS Interposer

by Anton Shilov on September 27, 2019 12:40 PM EST

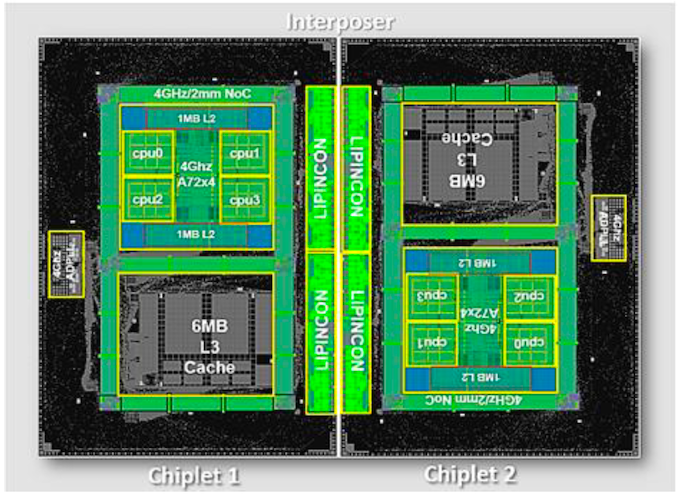

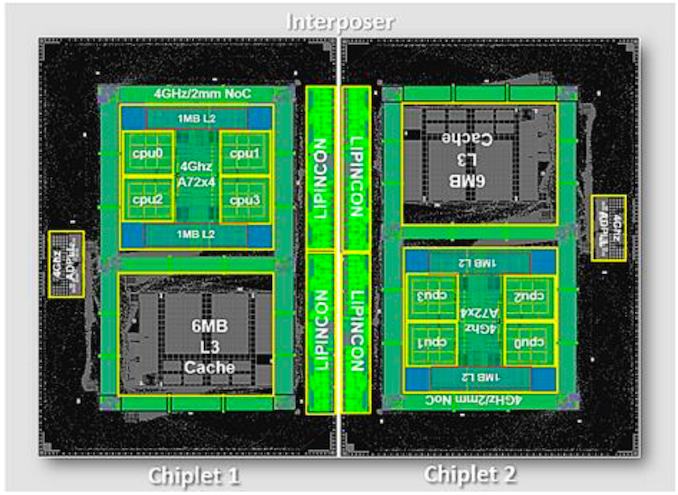

Arm and TSMC this week unveiled their jointly developed proof-of-concept chip that combines two quad-core Cortex-72-based 7 nm chiplets on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) interposer. The two chips are connected using the company’s Low-voltage-IN-Package-INterCONnect (LIPINCON) interface. The chip is meant to showcase potential of Arm’s and TSMC’s technologies for high-performance computing applications.

Large SoCs are hard and expensive to manufacture with decent yields using leading-edge process technologies these days. In fact, many elements of these SoCs do not need to be produced using the latest nodes at all. As a result, many chipmakers turn to the so-called chiplet design approach that relies on multiple smaller dies optimized for a particular function and produced using an appropriate process technology. Smaller dies afford better yields and better binning, allowing for a quicker return on investment. These smaller dies need to communicate with each other using a high-bandwidth low-latency and low-power inter-chiplet connections and the latter are the corner stone of any chiplet design.

The proof-of-concept system contains two chiplets made using TSMC’s N7 process technology and placed on a CoWoS interposer. Each chiplet features four Arm Cortex-A72 cores running at a whopping 4 GHz (this core was designed to run at <2 GHz frequencies inside mobile SoCs) that are interconnected using an on-die network-on-chip (NoC) mesh bus operating at 4 GHz. The cores are equipped with a 2 MB L2 cache (512 KB per core) as well as a 6 MB unified L3 cache.

The two chips are connected to each other using a LIPINCON die-to-die inter-chiplet connection that operates at 8 GT/s data transfer rate at 0.3 V and offers 320 GB/s bandwidth. When it comes to overall efficiency of LIPINCON on CoWoS, TSMC says that it features a 0.56 pJ/bit (pico-Joules per bit) power efficiency as well as a 1.6 Tb/s/mm2 (terabits per second per square millimeter) bandwidth density.

The proof-of-concept chiplet system was taped out in December 2018, and made in April 2019, so both Arm and TSMC had plenty of time to play with it. The chip will never be sold in volume, but it proves that technologies by the two companies can enable designers to build complex chiplet-based products with unique characteristics. THe companies are hoping that now this technology is proven that its customers will take advantage of it.

Related Reading:

- Hot Chips 31 Keynote Day 2: Dr. Phillip Wong, VP Research at TSMC (1:45pm PT)

- TSMC Announces Performance-Enhanced 7nm & 5nm Process Technologies

- TSMC: First 7nm EUV Chips Taped Out, 5nm Risk Production in Q2 2019

- TSMC Kicks Off Volume Production of 7nm Chips

Source: TSMC

26 Comments

View All Comments

guycoder - Friday, September 27, 2019 - link

Because Intel were never able to produce a viable 5G chipset and Apple had to sign a supply agreement with Qualcomm to cover the next couple of years. For the foreseeable future Apple will be using Qualcomm modems until they can fix the ex-Intel acquisition.Raqia - Friday, September 27, 2019 - link

After Apple's Intel modem unit purchase, they have enough engineers to integrate Qualcomm's solutions and new patents to help them negotiate down licensing costs, but not enough to develop their own soup-to-nuts solution in 5G. This new generation will be much more complex in RFFE interactions with the modem, and you can be sure that after their first dance with Apple, Qualcomm won't be giving them nearly as much help as they did during 4G under their collaborative work agreement over which the legal fracas initially started. (It is a testament to Apple's clout over the industry and its manufacturers that it almost pulled off what it did with Dialog, PowerVR, and GTAT with a company the size of Qualcomm, but ultimately it is also a testament to the strength of Qualcomm's IP and its lead in 5G solutions that Apple settled despite its deep war-chest and the engineering aid of the similarly deep pocketed Intel.)If Apple doubles their modem engineers and acquires an RFFE company such as Skyworks or Qorvo, then they would be getting serious about bringing an implementation in house, but it is very difficult to create a cellular implementation that is competitive with Qualcomm and rumors have it that Apple's internal timeline for such a solution is the mid 2020s (iirc 2023.) A purchase like this may come to pass as Qualcomm recently purchased their stake in their TDK 360 venture and will likely increase their content share of phones by becoming the reference design for many 5G solutions encompassing modem and RFFE, thus threatening the business of smaller RFFE companies in the next 5 years.

flgt - Friday, September 27, 2019 - link

It seems Apple would draw the line and not be bothered with an RFFE. It’s a bit of a commodity even in 5G. Skyworks and Qorvo both sell a lot of non-handset parts that Apple probably wants no part in supporting.Dragonstongue - Saturday, September 28, 2019 - link

15 stage is "kind of long" however, if both these 2 chips "talk nicely" to each other, this "real impact" might be ~10 stage or less (tandem compute .. I am call this way.. am sure there proper term .. medicine brain here not help.maybe they dd A72 as the wires etc were "easier" to work with, vs maybe one that had been "clipped" to get highest possible performance (like AMD did with Radeon 4870 to 4890 .. same thing, just clip etc wire, ramp clocks, feed slight different power...new product.

maybe this is similar, take a "4870" clip extra wires when they go to RTM so effectively becomes a 4890..same "sauce" even faster as they had time to "tweak and tune"

--------------

odd that Ryzen (going my way of thought) is/has as many issue as did/does, maybe they forgot to "clip the wires"

something along them lines......

interesting..seems this is the "future path" all compute folks MUST take as the die size goes down, will be slower but able to do more (little bit more latency)

am sure the makers of these things pull their hair out constantly till they "oh crap, that is what issue was"

Ask Intel and Nvidia ... the ones who can do no wrong as hurting something bad overall, compared to what should (this what happens when NOT pay attention to customers who keep your business alive... they must have forgot this... MSFT sure as hell has...Apple is very lost cause at this point for "consumer" ... sandwich cart service is ok for sandwich cart....not for hundreds if not millions $$$$$$$$$$ product purchase......

not your sandwich once WE bought it you fools....am I right or am I right?

TheinsanegamerN - Monday, September 30, 2019 - link

rather long 15 stage pipeline*laughs in netburst*

eastcoast_pete - Friday, September 27, 2019 - link

This is a very Interesting proof of concept, and especially attractive for situations where many cores/threads are highly desirable, and both cost and power consumption are important. Whoever gets the chiplets-on-interconnects just right is in a great position to sell many of them. If this works, ARM will make even more money for licenses, and TSMC probably doesn't mind getting lots of orders to fab the chiplets and interconnects. I wonder if "closed" shops like Anapurna (Amazon) are already developing their implementations.RSAUser - Friday, September 27, 2019 - link

It would be highly strange if they weren't as the entire industry has been trying to move in that direction for years, especially after AMD managed to pull it off so successfuly.The question now will be the who can figure out ways that will bypass patents or patent a high performance feature variation.

eastcoast_pete - Friday, September 27, 2019 - link

Doesn't have to be a bypass of the patents involved here. I see this more as a demonstration or proof-of-concept for tech that can be licensed, and maybe even at decent rates, as long as you fab them with TSMC.mappu04 - Friday, September 27, 2019 - link

Showcased in June 2019 at the VLSI Symposium Japan. You can also read wikichip coverage at https://fuse.wikichip.org/news/2446/tsmc-demonstra... .It is interesting to see so many new A72 designs in 2019, i guess TSMC likes them a lot (maybe they had a special license to the architecture?). For instance there was also the Xilinx versal, and Huawei's new 64-core thing, both A72 on TSMC in 2019.

Also the raspi 4 but that's probably just cost. Perhaps the A72 is a lot lot lot cheaper or maybe the vhdl is just floating around on github somewhere

eastcoast_pete - Friday, September 27, 2019 - link

Thanks for the link, very interesting indeed. A key feature from my POV is the low power cost per bit. The TSMC interconnect is not as fast as AMD's infinity fabric (8 GT/s vs 10.6 GT/s for IF), but only about a quarter of the energy per bit. And, for HPC, those picojoules per bit add up in a hurry.