PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

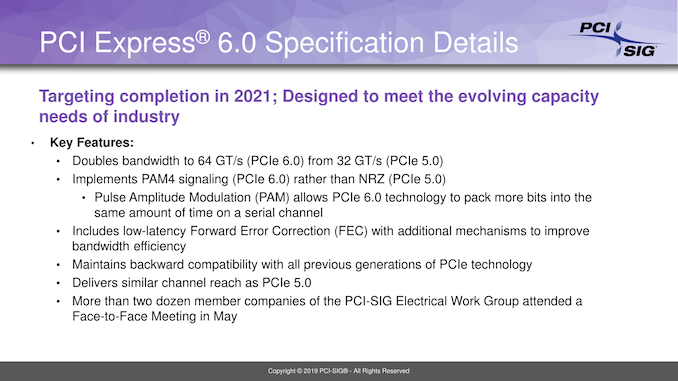

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

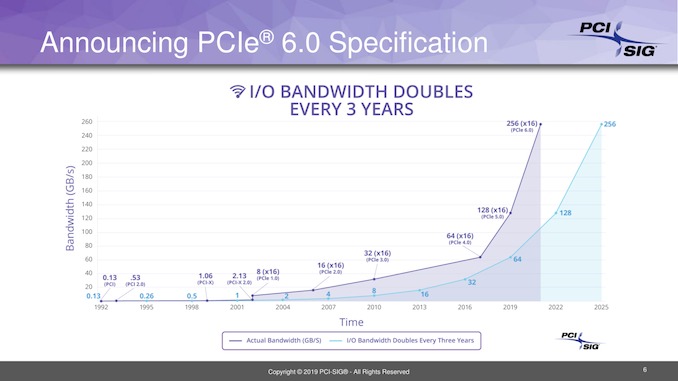

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

FreckledTrout - Friday, February 21, 2020 - link

No PCIe 5.0 is not dead. PCIe 4.0 will live on in desktops and slowly make its way into laptops at some point. It's just PCIe 5.0 and now PCIe 6.0 have so much bandwidth their use cases are server related. You will not see Intel or AMD with greater than PCIe 4.0 in non-server CPU's in a very long time, think 5 years out and that may still be early.Diogene7 - Friday, February 21, 2020 - link

I really, really wish for a quick implementation of PCIe 5.0 in consumers chip as it might help bring protocols that relates to Non Volatile Memory (NVM) like CXL, Gen-z,...A successor to the 7nm Qualcomm Snapdragon 8cx, done in 5nm with 5G and support for Non-Volatile-Memory (NVM) would enable many innovations to happen...

antonkochubey - Friday, February 21, 2020 - link

AM2 was PCIe 2.0AM3 was PCIe 3.0

AM4 is [up to] PCIe 4.0

and AM5 is coming in a year or two ;)

p1esk - Friday, February 21, 2020 - link

It might well be true that I will be 5 years until we see something better than 4.0, but my point is we are just starting to transition to 4.0 right now, so it will be a while until any major players decide to start planning for the next thing. When they do, 6.0 draft will be finalized, and it just won't make any sense to choose 5.0 spec when 6.0 spec is ready.Intel might be planning to skip 4.0 and go to 5.0, and if they do, it's will be a bad move, because AMD is most likely going to 6.0 after 4.0, so they will again be ahead when they release it.

mode_13h - Friday, February 21, 2020 - link

LOL. Unless you're buying server hardware, you won't have any option other than 4.0.evernessince - Monday, February 24, 2020 - link

It's probably prudent to point out that it would be a bad idea for a company that is making a chipset like AMD or Intel to skip PCIe 5.0. Just like PCIe 4.0 over 3.0, the number of wires in the motherboard increases dramatically as does the chipset's power consumption. If you skip a generation you are setting yourself up for more issues as you now have to find space for drastically more interconnects and somehow have to make your chipset 4 times as power efficient.Given that AMD had to increase the number of layers on X570 motherboards and the power consumption is high (15w), I don't see PCIe 6.0 being a good solution anytime soon. First we need to see PCIe 4.0 with lower power consumption and without the requirement of adding more PCB layers (which is expensive). Then we can start talking about PCIe 5.0 and eventually PCIe 6.0.

mode_13h - Monday, February 24, 2020 - link

From what I've read, going from PCIe 4.0 to 5.0 is even more expensive (in terms of PCB costs) than going from 3.0 to 4.0.romrunning - Friday, February 21, 2020 - link

The new 6.0 standard is changing to "pulse amplitude modulation with 4 levels (PAM-4) encoding" rather than NRZ - "non-return to zero." Since they are touting backwards compatibility, it seems like new PCIe 6.0 components will need to be able to both encode transfers in NRZ when part of a < 6.0 chain, and encode in the new PAM4 format only used with components that are 6.0 ready.I'm guessing it will take a bit more work to go to 6.0 than it will to go to 5.0. Who knows, perhaps putting any < 6.0 component into a 6.0 slot will stop your 6.0 components from reaching their maximum speed.

With all that, why not just skip 5.0 & go straight to 6.0? (shrug)

Billy Tallis - Friday, February 21, 2020 - link

PCIe uses point to point links to form a packet switched network. The speed and width of one link has no effect on the speed or width that gets negotiated for another link elsewhere in the system. You will be able to have a PCIe 6 link operating between a peripheral device and a PCIe switch even if the link between that switch and the CPU is operating at gen5 or earlier speeds. You will be able to use PCIe 6 speeds in one expansion slot even if the device in the next slot is running at a lower speed. This is how PCIe compatibility has always worked.The only things that will force a slower connection between two endpoints that both support a particular generation of PCIe are: inadequate analog signal quality (usually due to connector insertion loss), or older-generation redrivers or retimers (only found in servers so far).

romrunning - Friday, February 21, 2020 - link

Ah, that's good. I'm glad we're not back to the days of one component forcing the whole bus to a slower speed.