PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

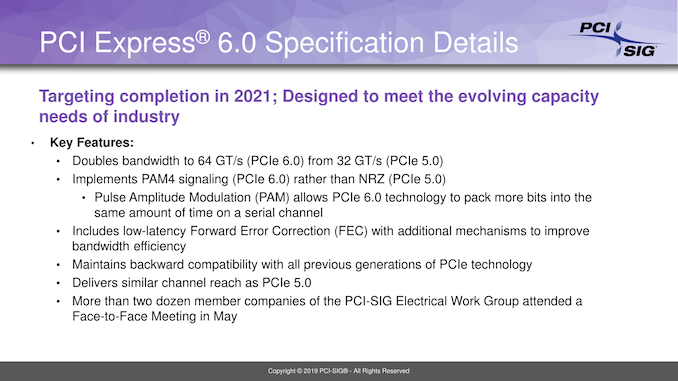

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

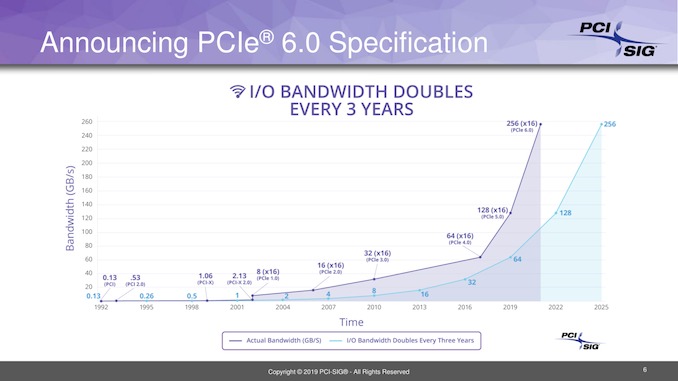

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

chophshiy - Friday, February 21, 2020 - link

Eventually. Notice how interfaces like USB 3.x/4 are getting shorter standard cables, heavier shielding, more expensive. Same principles.surt - Saturday, February 22, 2020 - link

Yes, and that's exactly why intel is massively investing in photonics and letting their other technologies lag.mode_13h - Saturday, February 22, 2020 - link

Perhaps, but they killed off Omnipath.name99 - Friday, February 21, 2020 - link

aka "given the slow adoption of PCIe by Intel"...Which is resolved in one of two ways:

- either Intel gets their act together AND/OR

- the competitors for whom PCIe6 matters (server/data warehouse, so AMD, Graviton, Nuvia, Ampere, ...) will provide PCIe 6 instead.

mode_13h - Friday, February 21, 2020 - link

Intel would already have PCIe 4.0-enabled server chips on the market, if their 10 nm didn't suck so hard.Santoval - Friday, February 21, 2020 - link

2021 is the target year of the final release of the PCIe 6.0 spec, not of any products. No PCIe 6.0 products will be available next year, except perhaps some testing / developing / prototyping kits. The final spec of PCIe 5.0 was released on May 2019, and we've still seen no PCIe 5.0 products - with the exception, I think, of a couple of Intel FPGAs which are for a very specialized market.So, at best, 2020 will be the year PCIe 4.0 becomes widely available. Then in 2021 we might get the first PCIe 5.0 products, with wide availability in 2022. Hence the earliest possible release of PCIe 6.0 should be in 2023 (limited), with wide availability in 2024. This assumes that new PCIe versions will be released every 2 years on average. If they're instead released every 3 years both PCIe 5.0 and PCIe 6.0 will be pulled back even further.

Santoval - Friday, February 21, 2020 - link

p.s. PCIe 6.0 products will almost certainly get delayed more than PCIe 5.0 products due to a radically changed design. PCIe 1.0 to 5.0 uses NRZ signaling and no error correction. So at a low level they are the same protocol, just each new version is clocked higher.PCIe 6.0 switches to PAM4 (only for PCIe 6.0 mode) and also employs Forward Error Correction (FEC), because PAM4 signaling is less robust and thus more prone to cross talk and interference. Since PCIe 6.0 retains backward compatibility with all previous PCIe versions, this means that NRZ support is also required.

So all PCIe 6.0 devices and controllers are required to support two signaling modes, PAM4 for PCIe 6.0 and NRZ for everything else. It goes without saying that this is going to complicate the implementation, deployment and probably the cost of PCIe 6.0 devices quite a bit. It doesn't help that PAM4 signaling is weaker, particularly at the high clocks the PCIe 6.0 mode requires.

The reason they moved to PAM4 was to put a brake on the clock increases. PAM4 has twice the bits of NRZ (it's like moving from SLC to MLC flash), so for PCIe 6.0 they didn't need to increase clocks over PCIe 5.0

descendency - Saturday, February 22, 2020 - link

It won't be available in a product. It will be ratified as a standard (v1.0)... but you likely won't see it in consumer products for years.haukionkannel - Friday, February 21, 2020 - link

From spefication to full product... can take a year or more. But I would not be surpriced that if my next upgrade from 5 years from now could have pci 6.0 :)mode_13h - Friday, February 21, 2020 - link

Only if you're buying a server board.