The Bulldozer Review: AMD FX-8150 Tested

by Anand Lal Shimpi on October 12, 2011 1:27 AM ESTThe Pursuit of Clock Speed

Thus far I have pointed out that a number of resources in Bulldozer have gone down in number compared to their abundance in AMD's Phenom II architecture. Many of these tradeoffs were made in order to keep die size in check while adding new features (e.g. wider front end, larger queues/data structures, new instruction support). Everywhere from the Bulldozer front-end through the execution clusters, AMD's opportunity to increase performance depends on both efficiency and clock speed. Bulldozer has to make better use of its resources than Phenom II as well as run at higher frequencies to outperform its predecessor. As a result, a major target for Bulldozer was to be able to scale to higher clock speeds.

AMD's architects called this pursuit a low gate count per pipeline stage design. By reducing the number of gates per pipeline stage, you reduce the time spent in each stage and can increase the overall frequency of the processor. If this sounds familiar, it's because Intel used similar logic in the creation of the Pentium 4.

Where Bulldozer is different is AMD insists the design didn't aggressively pursue frequency like the P4, but rather aggressively pursued gate count reduction per stage. According to AMD, the former results in power problems while the latter is more manageable.

AMD's target for Bulldozer was a 30% higher frequency than the previous generation architecture. Unfortunately that's a fairly vague statement and I couldn't get AMD to commit to anything more pronounced, but if we look at the top-end Phenom II X6 at 3.3GHz a 30% increase in frequency would put Bulldozer at 4.3GHz.

Unfortunately 4.3GHz isn't what the top-end AMD FX CPU ships at. The best we'll get at launch is 3.6GHz, a meager 9% increase over the outgoing architecture. Turbo Core does get AMD close to those initial frequency targets, however the turbo frequencies are only typically seen for very short periods of time.

As you may remember from the Pentium 4 days, a significantly deeper pipeline can bring with it significant penalties. We have two prior examples of architectures that increased pipeline length over their predecessors: Willamette and Prescott.

Willamette doubled the pipeline length of the P6 and it was due to make up for it by the corresponding increase in clock frequency. If you do less per clock cycle, you need to throw more clock cycles at the problem to have a neutral impact on performance. Although Willamette ran at higher clock speeds than the outgoing P6 architecture, the increase in frequency was gated by process technology. It wasn't until Northwood arrived that Intel could hit the clock speeds required to truly put distance between its newest and older architectures.

Prescott lengthened the pipeline once more, this time quite significantly. Much to our surprise however, thanks to a lot of clever work on the architecture side Intel was able to keep average instructions executed per clock constant while increasing the length of the pipe. This enabled Prescott to hit higher frequencies and deliver more performance at the same time, without starting at an inherent disadvantage. Where Prescott did fall short however was in the power consumption department. Running at extremely high frequencies required very high voltages and as a result, power consumption skyrocketed.

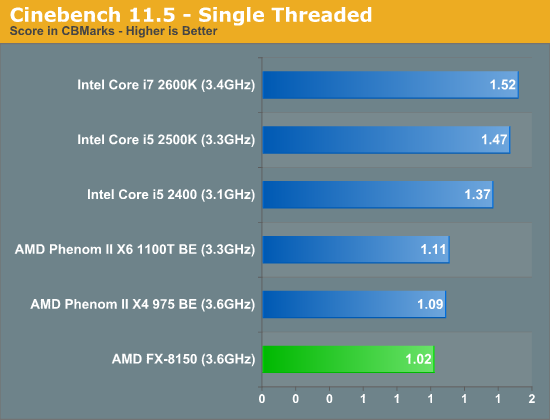

AMD's goal with Bulldozer was to have IPC remain constant compared to its predecessor, while increasing frequency, similar to Prescott. If IPC can remain constant, any frequency increases will translate into performance advantages. AMD attempted to do this through a wider front end, larger data structures within the chip and a wider execution path through each core. In many senses it succeeded, however single threaded performance still took a hit compared to Phenom II:

At the same clock speed, Phenom II is almost 7% faster per core than Bulldozer according to our Cinebench results. This takes into account all of the aforementioned IPC improvements. Despite AMD's efforts, IPC went down.

A slight reduction in IPC however is easily made up for by an increase in operating frequency. Unfortunately, it doesn't appear that AMD was able to hit the clock targets it needed for Bulldozer this time around.

We've recently reported on Global Foundries' issues with 32nm yields. I can't help but wonder if the same type of issues that are impacting Llano today are also holding Bulldozer back.

430 Comments

View All Comments

Ryan Smith - Wednesday, October 12, 2011 - link

Good point. Fixed.Marburg U - Wednesday, October 12, 2011 - link

they have a bloating cache with something wrong insidehttp://www.xbitlabs.com/images/cpu/amd-fx-8150/t5....

npp - Wednesday, October 12, 2011 - link

Sun went an even more extreme route regarding FP performance on its Niagara CPUs - as far as I remember, the first generation chip had a single FPU shared across eight cores. Performance was not even close to a dual-core Core 2 Duo at that time. So that was what I though when I first read about the "module" approach in Bulldozer maybe an year ago - man, this must be geared towards server workloads primary, it will suffer on the desktop. I guess FPU count = core count would have be more appropriate for the FX line.hasu - Wednesday, October 12, 2011 - link

Would this be a good candidate for web server applications because of its excellent multi-threaded performance? How about to host a bunch of Virtual Machines?sep332 - Wednesday, October 12, 2011 - link

I've also been wondering if running a lot of VMs would work better on this CPU. But I don't really know how you'd benchmark that kind of thing. Time and total energy consumption to serve 20,000 web pages from 12 VMs?magnetik - Wednesday, October 12, 2011 - link

I've been waiting for this moment for months and months.Reading the whole thing now...

themossie - Wednesday, October 12, 2011 - link

This processor is worse than the Phenom II X6 for most of my workloads. My next machine will be Sandy/Ivy Bridge.But... we haven't seen this clock ramp up yet. As Anand mentions on page 3 - Remember the initial Pentium 4s? The Williamette 1.4 and 1.5 ghz processors were clearly worse than the competition, to say nothing of the PIII line. In time the P4 consistently beat the much higher IPC AMD processors on most workloads, especially after introducing Hyper-threading. This really does feel like a new Pentium IV! Trying a design based on clock speed and one-upping Intel's hyperthreading by calling 4 '1.5' cores 8 (we hyperthread your hyperthreading!) - it will be a wild ride.

At this point, I don't see anyone beating Intel at process shrink and they're a moving target. But competitive pricing, quick ramp up and a few large server wins can still save the day. Dream of crazy clockspeeds :-)

themossie - Wednesday, October 12, 2011 - link

Upon further reflection...- Expect to see Bulldozer targeted towards servers and consumers who think "8 cores" sounds sexy, at least until clockspeed ramps up.

- Processor performance is not the limiting factor for most consumer applications. AMD will push APUs very heavily, something they can beat Intel at. Piledriver should drive a good price/performance bargain for OEMs, and for laptops may have idle power consumption in shouting distance of Sandy Bridge.

I'm more optimistic about AMD now. But my next machine will still be Sandy Bridge / Ivy Bridge.

wolfman3k5 - Wednesday, October 12, 2011 - link

I see people that say that they'll be waiting for Piledriver. Why not wait for AMD Drillbit, or AMD Dremel? How about AMD Screwdriver or AMD Nailpuller? Tomorrow my 2600K arrives. I'm done. I had a build ready with a ASUS 990FX ready for Bulldozer, but I will "bulldoze" the part back to NewEgg.I must admit, I was worried when I saw the large amounts of L2 cache before the launch. AMD engineers must have been taking the summer off, and decided to throw more cache at the problem. AMD needs a new engineering team. Why the hell can Intel get it right and they can't?

AMD, your CPU engineers are lazy and incompetent. I mean, it only took you "only" four years to get your own version of the Pentium 4.

The bottom line is that its time to fire your lazy retarded and incompetent engineers, and scout for some talent. That's what every other company does that wants to succeed, regardless of the industry. I mean, look at KIA and Hyundai for example, they went out and hired the best designers from Audi and the best engineers they could buy with money. Throw some more money at the problem AMD and solve your problems. And if those lazy fat fucks in Texas that you call engineers don't deliver, look somewhere else. Israel or Russia maybe? Who knows... Just my 2 cents.

IKeelU - Wednesday, October 12, 2011 - link

I know nothing of AMD employee's work ethic, but...their problems may have nothing to do with raw technical talent. But you are right about one thing - throwing money at a problem can be helpful, and that's likely why Intel has succeeded for so long. Intel has a lot of cash, and a lot of assets (such as equipment). They can afford the best design/debugging tools (whether they buy'em or make'em), which makes it much easier to develop a top product given the same amount of microchip engineering talent.And just because they're based in Texas doesn't mean their staff is all-American. Like most US tech firms, quite a bit of their talent was probably imported.