The Bulldozer Review: AMD FX-8150 Tested

by Anand Lal Shimpi on October 12, 2011 1:27 AM ESTThe Pursuit of Clock Speed

Thus far I have pointed out that a number of resources in Bulldozer have gone down in number compared to their abundance in AMD's Phenom II architecture. Many of these tradeoffs were made in order to keep die size in check while adding new features (e.g. wider front end, larger queues/data structures, new instruction support). Everywhere from the Bulldozer front-end through the execution clusters, AMD's opportunity to increase performance depends on both efficiency and clock speed. Bulldozer has to make better use of its resources than Phenom II as well as run at higher frequencies to outperform its predecessor. As a result, a major target for Bulldozer was to be able to scale to higher clock speeds.

AMD's architects called this pursuit a low gate count per pipeline stage design. By reducing the number of gates per pipeline stage, you reduce the time spent in each stage and can increase the overall frequency of the processor. If this sounds familiar, it's because Intel used similar logic in the creation of the Pentium 4.

Where Bulldozer is different is AMD insists the design didn't aggressively pursue frequency like the P4, but rather aggressively pursued gate count reduction per stage. According to AMD, the former results in power problems while the latter is more manageable.

AMD's target for Bulldozer was a 30% higher frequency than the previous generation architecture. Unfortunately that's a fairly vague statement and I couldn't get AMD to commit to anything more pronounced, but if we look at the top-end Phenom II X6 at 3.3GHz a 30% increase in frequency would put Bulldozer at 4.3GHz.

Unfortunately 4.3GHz isn't what the top-end AMD FX CPU ships at. The best we'll get at launch is 3.6GHz, a meager 9% increase over the outgoing architecture. Turbo Core does get AMD close to those initial frequency targets, however the turbo frequencies are only typically seen for very short periods of time.

As you may remember from the Pentium 4 days, a significantly deeper pipeline can bring with it significant penalties. We have two prior examples of architectures that increased pipeline length over their predecessors: Willamette and Prescott.

Willamette doubled the pipeline length of the P6 and it was due to make up for it by the corresponding increase in clock frequency. If you do less per clock cycle, you need to throw more clock cycles at the problem to have a neutral impact on performance. Although Willamette ran at higher clock speeds than the outgoing P6 architecture, the increase in frequency was gated by process technology. It wasn't until Northwood arrived that Intel could hit the clock speeds required to truly put distance between its newest and older architectures.

Prescott lengthened the pipeline once more, this time quite significantly. Much to our surprise however, thanks to a lot of clever work on the architecture side Intel was able to keep average instructions executed per clock constant while increasing the length of the pipe. This enabled Prescott to hit higher frequencies and deliver more performance at the same time, without starting at an inherent disadvantage. Where Prescott did fall short however was in the power consumption department. Running at extremely high frequencies required very high voltages and as a result, power consumption skyrocketed.

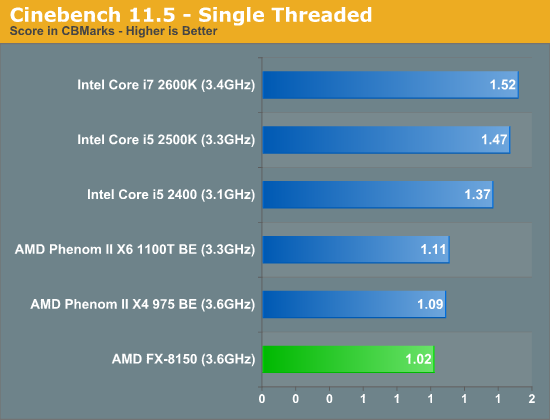

AMD's goal with Bulldozer was to have IPC remain constant compared to its predecessor, while increasing frequency, similar to Prescott. If IPC can remain constant, any frequency increases will translate into performance advantages. AMD attempted to do this through a wider front end, larger data structures within the chip and a wider execution path through each core. In many senses it succeeded, however single threaded performance still took a hit compared to Phenom II:

At the same clock speed, Phenom II is almost 7% faster per core than Bulldozer according to our Cinebench results. This takes into account all of the aforementioned IPC improvements. Despite AMD's efforts, IPC went down.

A slight reduction in IPC however is easily made up for by an increase in operating frequency. Unfortunately, it doesn't appear that AMD was able to hit the clock targets it needed for Bulldozer this time around.

We've recently reported on Global Foundries' issues with 32nm yields. I can't help but wonder if the same type of issues that are impacting Llano today are also holding Bulldozer back.

430 Comments

View All Comments

kiwidude - Wednesday, October 12, 2011 - link

I think this shows what a great job Intel have been doing more than confirming your insulting comment about AMD engineers.JohanAnandtech - Wednesday, October 12, 2011 - link

"Brand new and spanking Bulldozer has it roots in ancient K6"There is some K7 heritage left, but I can not see in any way how this CPU relates to the K6! The K6 had a very short pipeline, a unpipelined FPU for example.

As when it comes to the server market: AMD seems to have overclocked and cherry picked the 3.6 GHz FX-8100. For the desktop market, clockspeed rules, so AMD didn't care too much about power consumption.

For the server market, they can go with lower clocked 95 W TDP parts. These should have a much better performance/watt ratio. Also, the server market runs at 30-80% CPU load, the desktopmarket runs a few cores at 100%. So the powermanagement features will show better results in the server market.

The gaming software needs fast caches (latency!) as IPC is decent. The server software is more forgiving when it comes to cache latency as IPC is more determined by the number of memory accesses and thread synchronization. That is the reason why that L3 is so handy. I think you should wait to condemn bulldozer until it is has been benchmarked on our server benchmarking suite.

I am worried about the legacy HPC performance of this chip though.It will take some recompiling before the chip starts to shine in this market.

FunBunny2 - Wednesday, October 12, 2011 - link

Had to get this far in the comment thread for sanity. Clearly, AMD (and one may disagree) has chosen to go for superior integer performance in a threaded architecture. D'oh! So what? It means they don't give a rat's rectum about gamers. They care a whole lot about application and database servers. They also accept the fact that single threaded is dying, so just kill it.Makaveli - Wednesday, October 12, 2011 - link

I stayed up and read this its 2 in the morning excellent review as always anand.But instead of back to the future its back to the P4???

Why AMD WHY for the love of everything holy!

Sind - Wednesday, October 12, 2011 - link

Disappointing.. I hope they can get it together with the aggressive road map.wolfman3k5 - Wednesday, October 12, 2011 - link

I know, right. I'm also patiently waiting for the AMD Bendover architecture. Maybe it will be competitive, who knows...kiwidude - Wednesday, October 12, 2011 - link

Hi, the CPU Specification Comparison chart has incorrect info listed under X6 1100T and X4 980 NB clocks. Great review as always love your work.wolfman3k5 - Wednesday, October 12, 2011 - link

NewEgg doesn't even have any Bulldozers in stock, at all. Not the AMD FX 8150 or AMD FX 8120. I guess that no one is in a hurry to grab one...enterco - Wednesday, October 12, 2011 - link

Hell, Amazon UK doesn't have any Bulldozer neither...ckryan - Wednesday, October 12, 2011 - link

Maybe Newegg filed them under Server CPUs where BullDozer belongs.