An Introduction to Semiconductor Physics, Technology, and Industry

by Joshua Ho on October 9, 2014 3:00 PM EST- Posted in

- Semiconductors

- CMOS

- Physics

- Industry

- Technology

Manufacturing: Making Wafers

To make a computer chip, it all starts with the Czochralski process. The first step of this process is to take extremely pure silicon and melt it in a crucible that is often made of quartz. Doping material can also be added at this stage, to change the properties of the final crystal. Once this is done, a single seed crystal is dipped into the molten silicon, then carefully pulled up with a specific rotation rate. This produces a piece of monocrystalline silicon that is then sliced into wafers. These wafers can be up to 300mm in diameter at present and around .75mm thick, and they are polished to ensure that the surface is as regular and flat as possible.

Manufacturing: Photolithography/FEOL

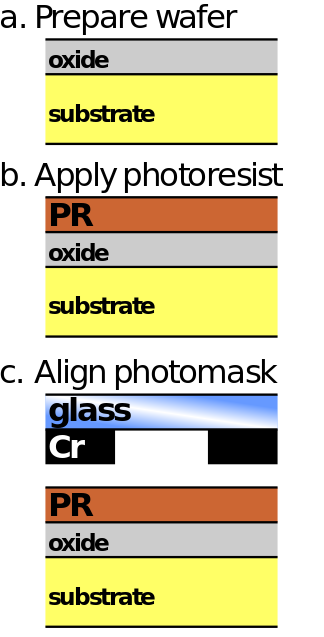

Photolithography Etching Process / Cmglee / CC BY SA

Scanning Stepper Middle Exposure / Everyguy

Once this is done, the wafer is prepared for photolithography. An oxide layer on top of the silicon wafer is grown, and then the entire wafer is cleaned to remove contaminants. Once this is done, an adhesion promoter is applied to ensure that the photoresist will stick properly to the wafer. The photoresist is then applied by dispensing a solution of photoresist on to the wafer. The wafer is then spun at extremely high speeds for around half a minute to a minute. Once this is done, the wafer is then baked on a hot plate to get rid of the remaining solvent. In preparation for the exposure, a reticle/photomask for one layer of the process is loaded, and aligned with the wafer. In order to increase resolution, an exposure slit is used to optimize for a smaller exposure area on the reticle/projection lens system, and aberration is reduced.

Once all of this preparation is done, the exposure process begins. Intense UV light (currently 193nm) is used to change the exposed photoresist to allow the developer to strip away the exposed area. As a quick aside, the fact that UV light is used to develop the regions to etch away means that only long wavelength light can be used in clean rooms, which gives the clean room a characteristic yellow lighting. Once this is done, the wafer is baked again. This process is done again in order to properly develop the photoresist.

Once the wafer is ready, developer is added. This strips away the photoresist from the exposed regions. The exposed oxide is then etched away. While this process can be done with a liquid agent, modern dry-etch processes ionize a gas in vacuum using an RF cavity that is then shot at the exposed oxide to avoid etching past the exposed portion of the oxide. Once this etching process is complete, the photoresist is removed either through plasma ashing or by washing it off with a resist stripper.

To summarize everything I just said, the process is effectively cleaning the wafer, applying photoresist, exposing the photoresist, developing the photoresist, etching the exposed oxide, then removing the remaining photoresist.

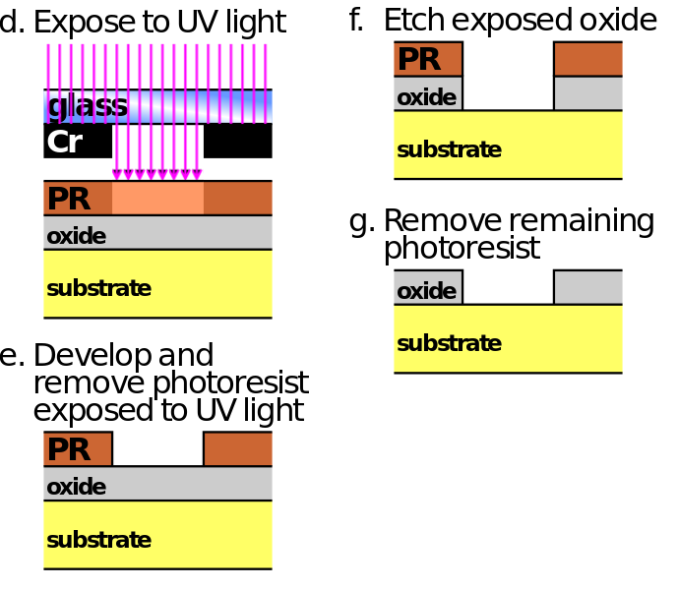

CMOS Fabrication Process / Cmglee / CC BY SA

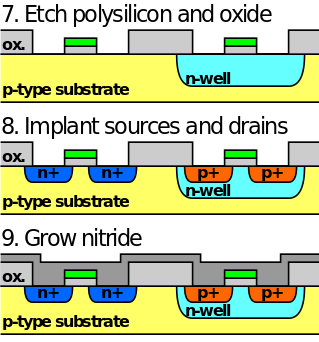

A modern wafer will undergo this process around 50 times or so before creating the final finished chip. You might want to know how all of this etching actually creates transistors, so we’ll once again go over the simplest case, the CMOS inverter. The first lithography pass is used to mark out the area so that we can deposit a well of n-doped silicon that the PMOS will use. Then, the oxide is grown again and a layer of polysilicon is deposited.

Another lithography pass is done to etch away parts of the oxide, then most of the polysilicon. This leaves a small piece in the center of the exposed substrate composed of silicon dioxide, then polysilicon. If this sounds familiar, it’s because this is the structure of the gate. Once this is done, ion implantation is used to create the sources and drains. The best description I can give of ion implantation is taking an ion and accelerating it to high speeds to embed itself into the targeted area, which dopes the substrate. Once this is done, a layer of nitride is added to prevent further oxide growth, which is then etched again.

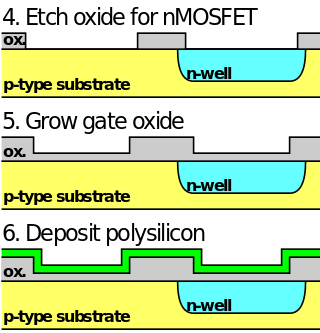

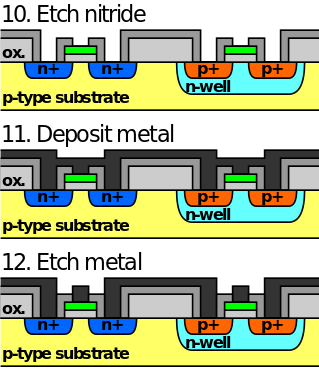

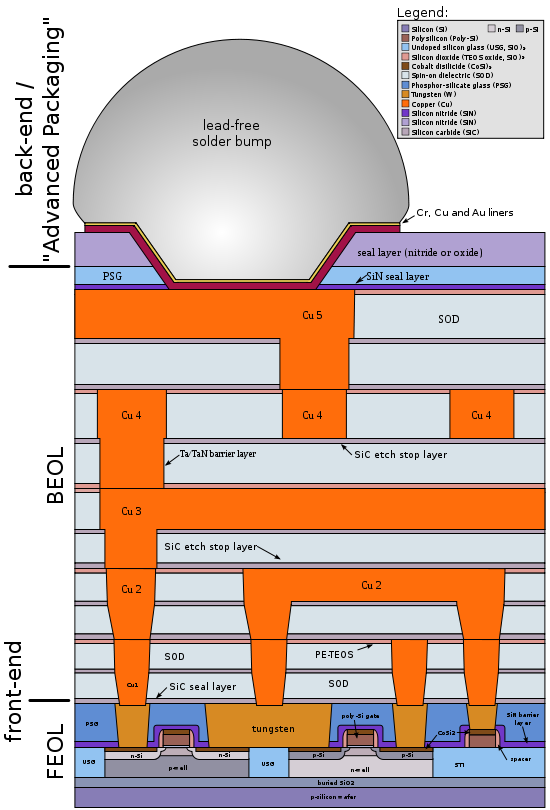

Manufacturing: Back End of Line and Back End of Chip

Yet we’re still not done with how the chip is made. We just finished going over what happens in front-end-of-line (FEOL) processing. Now it’s time to go over what happens at back-end-of-line (BEOL) processing. Once the nitride layer is finished, a layer of metal is deposited over the entire system. This layer is then etched again to finish the transistor fabrication process. The result is that all the correct components for source, drain, gate, and body are implanted with metal connectors for input and output for our hypothetical CMOS inverter.

In a real chip, as many as 12 layers are added in this process, which means repeating the metal deposition step 12 times. This step is where all of the transistors are wired together, along with interlayer connections (vias), capacitors (in DRAM), dielectric isolation, and chip to package connectors. Once BEOL processing is complete, the chip is packaged and ready to be used.

CMOS Chip Structure / Cepheiden / CC BY SA

Of course, this entire production process isn’t perfect. Along the way, the wafer is tested multiple times to ensure that there are no defects from a previous step. If there are too many defects on a wafer, the entire wafer must be thrown away to avoid wasting time and money on further processing. After the FEOL processing is complete, the chip is tested and binned using a wafer prober. After the entire chip is packaged, the chip is tested again to ensure that the entire package is fully functional. The packaging and final testing stages are also known as the back end of chip fabrication.

Recap

To review everything we’ve just gone over, we started with the physics of semiconductors. Then we moved on to the physics of transistors. After that, we went over how to make logic with these transistors. Finally, we went over how to actually make transistors with logic. This would be a good place to stop, but complacency is a terrible reason to do so.

The question now is how to make things faster with less power. To do this, we have to figure out how to make the feature size smaller, in order to pack more transistors closer together. To put things in perspective, 43 years ago in 1971 with the Intel 4004 we had a feature size of 10,000 nanometers. That’s around 455 times as large as the 22nm feature size of what we see in Intel’s Haswell CPUs. Now it’s time to find out how this was achieved.

77 Comments

View All Comments

Khenglish - Thursday, October 9, 2014 - link

Curving the wafer actually has major impacts on electronic operation. For example wafer bending is currently done by implanting Germanium into the wafer for PFETs. Because Ge is larger than Si, this causes the wafer to bend. This bend increases hole mobility making PFETs more conductive and faster, but slows down NFETs, thus manufacturers implant Ge only at PFET locations. This processes of bending the wafer by implanting Ge is strained silicon, and 1st started showing up around the 130nm era. It is done because for similarly sized transistors, NFETs are around 2.7x more conductive than PFETs without strained silicon.EMM81 - Monday, October 13, 2014 - link

There is definitely no curving or any wafer. Ge is used to strain the silicon crystal latice. Ge is in the same group on the periodic table and forms the same diamond cubic crystal structure. Grading a fraction of Ge (larger atoms longer bond lengths) into the Silicon latice the silicon bonds effectively get stretched (see image in article). This has a physical effect on the mobility of electrons and holes. Curving a wafer is a non-starter as NONE of the standard processing techniques would work...wafers have to be not only flat but ultra flat for litho optics, dry etch, wet etch spinners, ion implanters...hlovatt - Thursday, October 9, 2014 - link

Great article. More please!witeken - Thursday, October 9, 2014 - link

Awesome, thanks for the great article.However, 22nm doesn't have a single feature size of 22nm. It's just a name, and so are 28nm, 20nm, 16nm, 14nm,...

For example, the fins of 22nm are 8nm while the gate pitch is 90nm. (http://images.anandtech.com/doci/8367/14nmFeatureS...

Khenglish - Thursday, October 9, 2014 - link

When you hear 22nm, 32nm, 16nm, etc the number you are hearing is the smallest feature size that can be imprinted via lithography. This is not necessarily the smallest feature size than can be implemented on the process.EMM81 - Monday, October 13, 2014 - link

This is not true. Node size was loosely defined as the half pitch of either the poly-silicon gate or the tightest metal pitch. The node size designation however, has not followed the minimum half pitch for many technologies, from any of the fabs. Node size is now a purely marketing term. If a fab were to implement HKMG, strained silicon...these things would not necessarily have any effect on the dimensions of transistors but they would result in improvements to the chip performance. Density is only 1 component that plays into node designation these days and even then density of the transistors is being tightened by some fabs while leaving the density of the upper layers unchanged.Khenglish - Wednesday, October 15, 2014 - link

Again just because lithographic features can be made a certain size does not mean you make everything that size. Maybe there is just one minor feature that is really that size. I'm saying that process size is the minimum size that can cut by the ebeam into a lithography mask and transferred if the design calls for it. This is why when looking at a processor that the feature size is so hard to quantify. Just one feature at whatever they advertise can let them call it that number. Yes feature size doesn't need to have anything to do with density or performance and is mostly a marketing thing.Keisari - Thursday, October 9, 2014 - link

A very necessary article. Great initiative!martixy - Thursday, October 9, 2014 - link

There's probably something to be said about breezing through this(of my own free will moreover), while having such a hard time with the exact same material from the textbook.Go figure.

Murloc - Thursday, October 9, 2014 - link

It's meant to be intuitive and summarized in a limited amount of space. That's why it's easy to read. It has way less depth than a textbook.