The AMD Radeon RX 480 Preview: Polaris Makes Its Mainstream Mark

by Ryan Smith on June 29, 2016 9:00 AM ESTThe Polaris Architecture: In Brief

For today’s preview I’m going to quickly hit the highlights of the Polaris architecture.

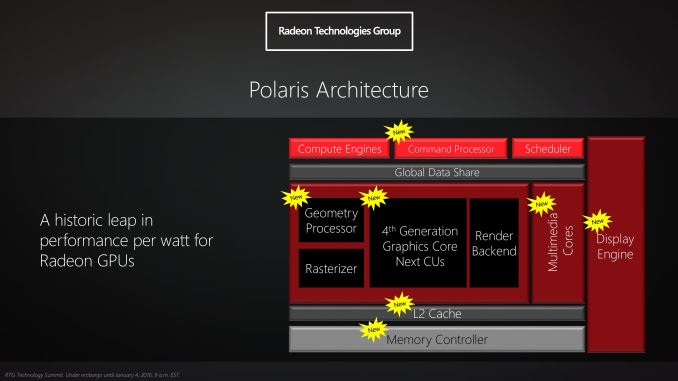

In their announcement of the architecture this year, AMD laid out a basic overview of what components of the GPU would see major updates with Polaris. Polaris is not a complete overhaul of past AMD designs, but AMD has combined targeted performance upgrades with a chip-wide energy efficiency upgrade. As a result Polaris is a mix of old and new, and a lot more efficient in the process.

At its heart, Polaris is based on AMD’s 4th generation Graphics Core Next architecture (GCN 4). GCN 4 is not significantly different than GCN 1.2 (Tonga/Fiji), and in fact GCN 4’s ISA is identical to that of GCN 1.2’s. So everything we see here today comes not from broad, architectural changes, but from low-level microarchitectural changes that improve how instructions execute under the hood.

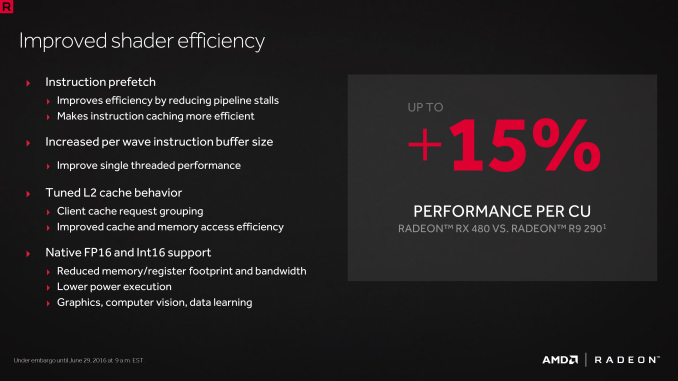

Overall AMD is claiming that GCN 4 (via RX 480) offers a 15% improvement in shader efficiency over GCN 1.1 (R9 290). This comes from two changes; instruction prefetching and a larger instruction buffer. In the case of the former, GCN 4 can, with the driver’s assistance, attempt to pre-fetch future instructions, something GCN 1.x could not do. When done correctly, this reduces/eliminates the need for a wave to stall to wait on an instruction fetch, keeping the CU fed and active more often. Meanwhile the per-wave instruction buffer (which is separate from the register file) has been increased from 12 DWORDs to 16 DWORDs, allowing more instructions to be buffered and, according to AMD, improving single-threaded performance.

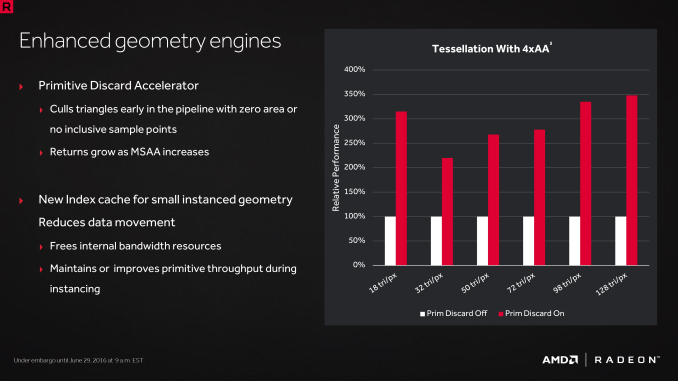

Outside of the shader cores themselves, AMD has also made enhancements to the graphics front-end for Polaris. AMD’s latest architecture integrates what AMD calls a Primative Discard Accelerator. True to its name, the job of the discard accelerator is to remove (cull) triangles that are too small to be used, and to do so early enough in the rendering pipeline that the rest of the GPU is spared from having to deal with these unnecessary triangles. Degenerate triangles are culled before they even hit the vertex shader, while small triangles culled a bit later, after the vertex shader but before they hit the rasterizer. There’s no visual quality impact to this (only triangles that can’t be seen/rendered are culled), and as claimed by AMD, the benefits of the discard accelerator increase with MSAA levels, as MSAA otherwise exacerbates the small triangle problem.

Along these lines, Polaris also implements a new index cache, again meant to improve geometry performance. The index cache is designed specifically to accelerate geometry instancing performance, allowing small instanced geometry to stay close by in the cache, avoiding the power and bandwidth costs of shuffling this data around to other caches and VRAM.

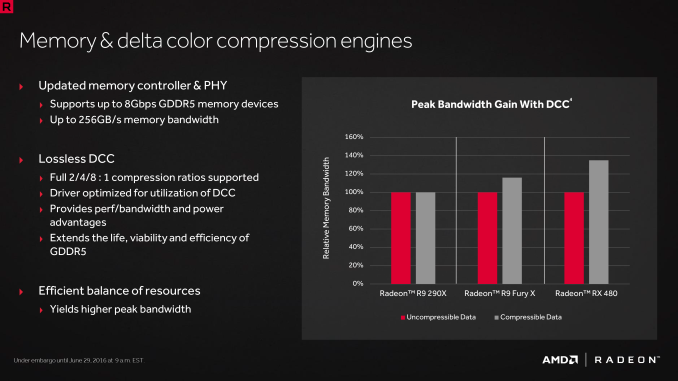

Finally, at the back-end of the GPU, the ROP/L2/Memory controller partitions have also received their own updates. Chief among these is that Polaris implements the next generation of AMD’s delta color compression technology, which uses pattern matching to reduce the size and resulting memory bandwidth needs of frame buffers and render targets. As a result of this compression, color compression results in a de facto increase in available memory bandwidth and decrease in power consumption, at least so long as buffer is compressible. With Polaris, AMD supports a larger pattern library to better compress more buffers more often, improving on GCN 1.2 color compression by around 17%.

Otherwise we’ve already covered the increased L2 cache size, which is now at 2MB. Paired with this is AMD’s latest generation memory controller, which can now officially go to 8Gbps, and even a bit more than that when oveclocking.

449 Comments

View All Comments

PeckingOrder - Wednesday, June 29, 2016 - link

What a massive F-up by AMD.evolucion8 - Wednesday, June 29, 2016 - link

Sure, cause AMD midrange GPUs are meant to replace previous high end of GPUs lolddriver - Wednesday, June 29, 2016 - link

In the chart, the AMD Radeon RX 480 (4GB) is listed as having 8 gigs of vram.ddriver - Wednesday, June 29, 2016 - link

I mean the "AMD Radeon GPU Specification Comparison" chart.SunnyNW - Wednesday, June 29, 2016 - link

Ryan Shrout of PCper said Every RX480 actually has 8GB of memory on the board..Like WTF...He further added that they sent bios to switch the cars between 4GB and 8GB. I understand the artificial prodcuct segmentation that often happens in tech but with the large number AMD hopes to sell that is A LOT of wasted memory! WOW what a waste they should have just had 8GB reference only and priced it 10 to 15 bucks less...Drumsticks - Wednesday, June 29, 2016 - link

This is only for the press. The retail 4GB cards have 4GB of VRAM, per the AMA on reddit.akamateau - Wednesday, June 29, 2016 - link

4 and 8gb are currently being released.Amazon here:

https://www.amazon.com/XFX-Radeon-Graphics-Cards-R...

Newegg here:

http://www.newegg.com/Product/Product.aspx?Item=N8...

akamateau - Wednesday, June 29, 2016 - link

2 RX 480 CRUSHES GTX 1080 for $200 less!!!basroil - Wednesday, June 29, 2016 - link

"2 RX 480 CRUSHES GTX 1080 for $200 less!!!"That's if any motherboards even support that configuration! Tests have shown that the card:

1) Draws closer to 165W, much higher than it's actual supported maximum power draw of 150W

2) ~80W of that is from the PCIe slot itself. Motherboards are only required to allow 75W for ALL PCIe slots. Either way it will overload the traces on cheaper boards.

Put those together and you have a nightmare fuel of either frying the mobo with >150W draw when even 2x1080 wouldn't hit 75W, or frying your PSU as the cards reroute power to the PCIe power cable and overload the 75W capable 6pins with double their rated amperage.

binarydissonance - Wednesday, June 29, 2016 - link

Or both the mobo and the PSU are supplying the same voltage and the power input is combined into a single bus... y'know... preventing the unlikely scenario you describe from ever possibly happening.