An Introduction to Semiconductor Physics, Technology, and Industry

by Joshua Ho on October 9, 2014 3:00 PM EST- Posted in

- Semiconductors

- CMOS

- Physics

- Industry

- Technology

Light Sources

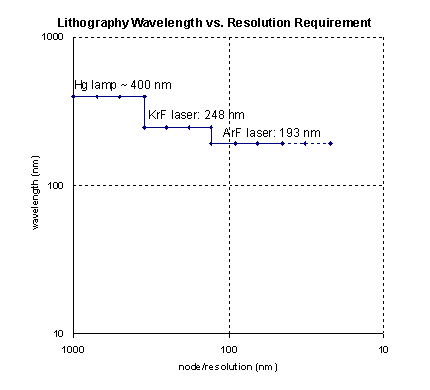

While many other technologies are tangentially related to shrinking feature size, one of the primary ways within the past four decades or so has been through smaller wavelengths of light. Shorter wavelengths mean higher resolution, much like how the electron microscope’s shorter de Broglie wavelength increased resolution over light microscopes. Thus, photolithography can increase in resolution by using light sources that generate shorter wavelengths.

Lithography Wavelength vs Resolution / Guiding light / CC BY SA

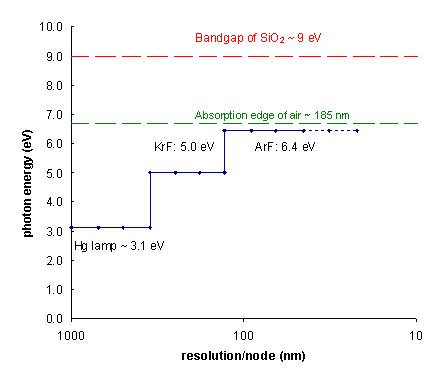

This progression has happened steadily over the years, starting with mercury lamps that produced UV light of around 400 nanometers. Once this was no longer sufficient, lasers became necessary in order to drive higher resolution and rate of production. The first was the krypton fluoride laser that generated a wavelength of 248nm, then argon fluoride to generate 193nm. Unfortunately, this is near the limit of what can be realistically used in an environment that contains air, as even 193nm is attenuated significantly. As seen in the photo below, in order to go lower for EUV and similar wavelengths, the lithography process must be done in a vacuum as otherwise air will absorb almost all of the energy emitted.

Photon Energy vs. Resolution / Guiding light / CC BY SA

Immersion Lithography

Immersion Lithography / Renesas

So the inevitable question is what could be done next. While different foundries adopt technologies at different times, one way to push resolution further is immersion lithography, which was done around the 65nm node to 32nm node. This is relatively simple, as what this effectively does is increase the numerical aperture of the optical system because the light from the source can be refracted better than before. This is done by immersing the wafer and projection lens in extremely pure water.

Of course, this is far from a simple task in practice. The deionized water must also have no gases present that could cause air bubbles between the lens and wafer, with extremely consistent temperature and pressure. Otherwise, the actual index of refraction in the water will change unexpectedly and cause defects in the lithography process. The 193nm light used in current lithography processes can also ionize the water and in turn cause reactions with the photoresist.

Unfortunately, with processes like EUV lithography it’s no longer possible to use this method to drive higher resolution and smaller feature size because the liquid used will generally absorb all of the energy emitted. However, it’s still possible to drive higher resolution with 193i technology by using fluids with a higher index of refraction, which is an area of exploration for further resolution increases.

Multiple Patterning

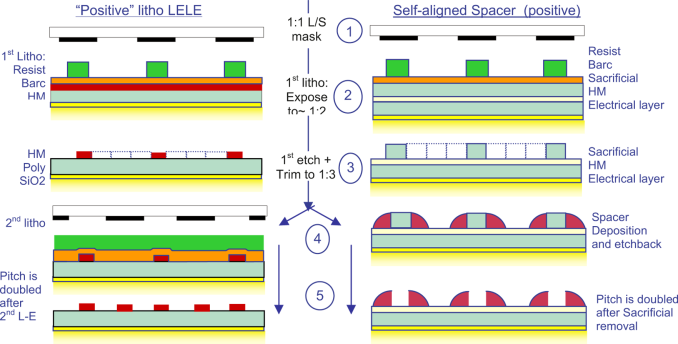

Multiple Patterning / SPIE

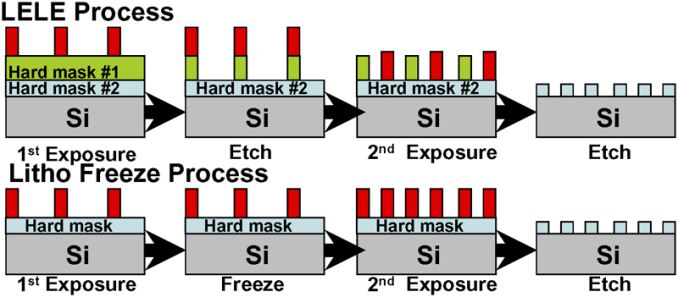

Another technique that can be used with EUV lithography is multiple patterning. While it’s “one” technique, the ways to implement multiple patterning are numerous. All have the same goal though. In essence, if a theoretical system can only provide sufficient resolution to draw two lines 64nm apart, it’s possible to double the resolution by printing another two lines 64nm apart by doing a second exposure. The result is four lines that are 32nm apart. There are a few ways to achieve this, which are known as litho-etch, litho-etch (LELE), litho-freeze, litho-etch (LFLE), and self-aligned double patterning (SADP).

LELE is rather simple in implementation and relies upon two separate photoresist layers. In the first pass, lithography is done on a hard mask, then developed. It’s important to use a hard mask, because in the second pass another layer of photoresist is applied, then exposed and developed. If there wasn’t a hard mask, the first pass would simply disappear when the second layer of photoresist is applied. LFLE is simply a modification of the LELE technique, where the hard mask is eliminated. After the initial lithography process, the photoresist is frozen by coating it with a chemical agent that is then baked and developed away, making it so that the first resist layer is separable from the second layer. Once this is done, a standard lithography pass is done to complete the process.

LELE & SOAP Patterning / SPIE

SADP is a very different way of doing things, but the end result is the same. The first step is doing a lithography/etch of dummy patterns that become the actual lines that are intended to be etched on the final pattern. Once this is done, a hard mask or similar material is deposited over the dummy patterns. After this, the hard mask is etched to expose the sidewalls that line the dummy patterns. Once all of this is completed, the dummy pattern is developed away and the exposed oxide is etched as usual. The result is that the lines are twice as close as before, and only one lithography pass was needed.

Unlike LELE and LFLE, there’s no need to be concerned about alignment because after the dummy pattern is set up, there’s no second exposure. This may be the reason why Intel's 22nm FinFET uses this process. Because the sidewall spacers are often created with hard mask materials, the resulting lines are also cleaner. This fact will become important, especially when discussing EUV and similar next generation lithography techniques.

While these techniques may sound like the perfect way to increase resolution, ultimately multiple patterning becomes increasingly expensive and difficult, especially because even a small misalignment between the two patterns can result in a wasted wafer. Multiple patterning also causes design restrictions that wouldn't occur with a true resolution increase in the lithography process because certain patterns become impossible with even order or odd order patterning processes.

Computational Lithography

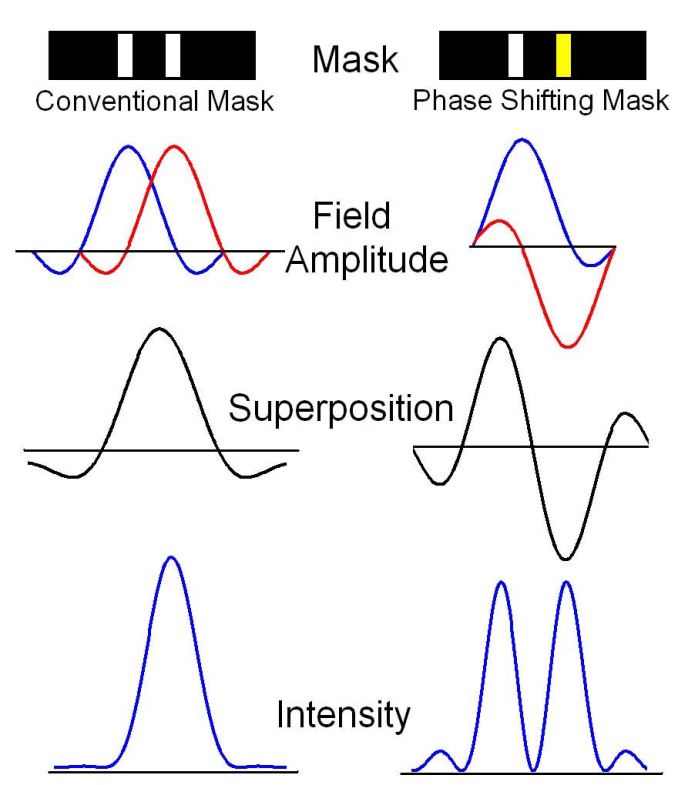

Phase Shifting Mask / Stanley H. Chan

While we’re still talking about (relatively) low hanging fruit, I want to cover two other methods that are used to enhance resolution. The first is phase shifting masks. Rather than focusing upon wafer-level changes, this improves the reticle/mask itself. In short, this exploits the wave nature of light. There are two types of phase-shifting masks, and the first is an alternating phase-shift mask. This alters the thickness of the mask in some regions, which induces a phase-shift on the light waves that pass through it. As a result, there is interference with light from unmodified regions, which means that higher contrast can be achieved between the exposed and unexposed regions. The other type is the attenuated phase-shift mask, which only lets small amounts of light pass through that can interfere with the light coming from transparent regions.

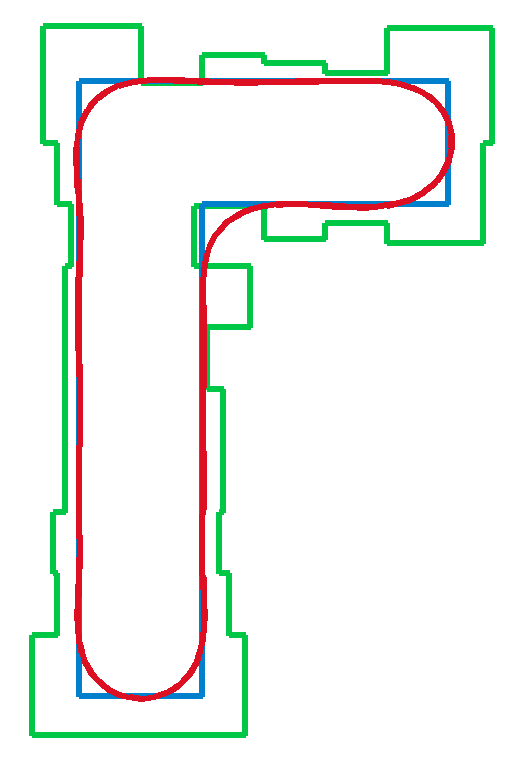

Source Notes: Intended pattern in blue, OPC-corrected in green, final pattern in red.

Optical Proximity Correction / LithoGuy

The second is optical proximity correction, or OPC. One of the imperfections in the lithography process that we haven’t talked about until now is that what is drawn on the photomask/reticle is not translated exactly on to the photoresist. In reality, line widths vary greatly depending upon how dense the pattern around the line is; lines don’t end where they do on the mask, and the ends of lines are much thicker than the middle. OPC compensates for all of these effects and computes the photomask needed to achieve a layout close to the intended design.

Review

Summarizing things again, there are multiple techniques used to increase resolution to fabricate smaller transistors. By using lower wavelengths of light, multiple patterning techniques, and computational lithography techniques like phase shifting masks and optical proximity correction, we’ve managed to make it all the way down to 22 nanometer feature sizes. With the launch of Intel's Core M, we’ve made another jump down to 14 nanometers using the same light source that we did at 90 nanometers.

77 Comments

View All Comments

PrayForDeath - Thursday, October 9, 2014 - link

Articles like this are the reason why I visit Anandtech *starts reading*monstercameron - Thursday, October 9, 2014 - link

Most of this is abit over my head. If possible maybe next time use literary devices to explain these technologies. Also what about tsv and stacked dice?Homeles - Thursday, October 9, 2014 - link

Is there anything in particular you're struggling with?Kutark - Sunday, October 12, 2014 - link

I'm with him. I need someone to take some paper and some crayons and draw me a picture hahaha.climber07 - Monday, October 13, 2014 - link

It isn't an easy concept to grasp at first. Transistors generally operate in two states. On and off. They require a certain voltage to make them come on. For the sake of simplicity, these two states are 1's and 0's (data bits). They form logic gates in circuits (if this and this or this then it equals this). The material that they use for transistors (and diodes) are silicon. Silicon requires approximately .7 volts to forward bias (allow current to flow and turn on). There are literally thousands of websites and graphic representations of basic transistor theory to explore. Try "How Stuff Works dot com".Burn2learn - Friday, November 14, 2014 - link

How can this be over your head if your aware of thru silicon vias (tsv)adityarjun - Thursday, October 9, 2014 - link

Awesome! Hope to see a lot more of such articles for learners.seanleeforever - Thursday, October 9, 2014 - link

pretty much a brief review of my E.E college course back in the days.great article.

A5 - Thursday, October 9, 2014 - link

Yep. Getting bad SRH equation flashbacks now :-pjjj - Thursday, October 9, 2014 - link

Just took a quick look at the article for now so maybe i've missed it but i don't think you mention 3D at all (actual 3D not FinFET or 2.5D packaging).And here comes the crazy question, was looking at the CMOS Chip Structure pic and wondered if anyone has tried to make curved (on 1 or even 2 axis) chips just to have more room on the extremal layers. As i wrote this i remembered the Sony curved image sensor and i wonder how would they fab that if they actually make it into a real product.Any clue?