AMD Gives More Zen Details: Ryzen, 3.4 GHz+, NVMe, Neural Net Prediction, & 25 MHz Boost Steps

by Ian Cutress on December 13, 2016 4:00 PM EST

In the eternal battle to drive more details out of AMD ahead of the full launch of its new Zen microarchitecture based CPUs, today AMD is lifting the lid on some new features in order to whet the appetite (and appease the hype-train, perhaps) and that will be part of the product launch. We now have new details on the brand naming, some platform details, and a high-level overview of what will be the key points being promoted when it comes to market.

We’ve covered a lot of Zen, from the initial announcement to some of the microarchitecture details at Hot Chips through to discussing the utility of singular benchmark data and then what might be happening on the server side through a detailed analysis of motherboards on display. A lot of us want it out already, and when it does, it will come out under the brand ‘Ryzen’.

Ryzen and AM4

It is pronounced ‘Rye-zen’, not ‘Riz-zen’, to clarify.

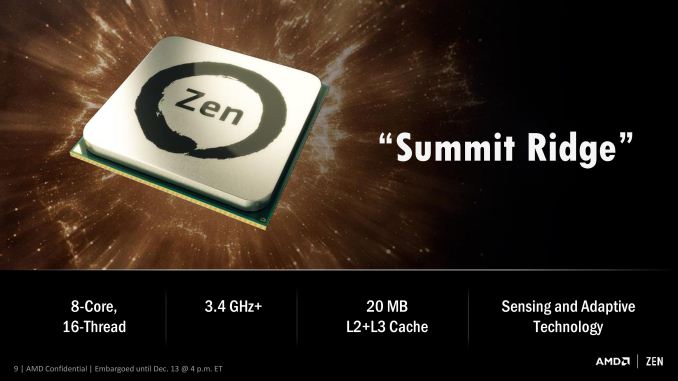

As expected, there will be several SKUs in the brand, although AMD is not releasing many details aside from the cache arrangement of the 8-core, thread chip (which we already knew was 4MB of L2 + [8+8] MB of L3 victim-cache), and that the base clock for the high-end SKU will be at least 3.4+ GHz. The fact that AMD says ‘at least’ dictates that they are still deciding exactly what to do here, although a similar thing was said leading up to the launch of Polaris-based RX cards (though that’s a different department).

We know that Ryzen will use the AM4 platform, shared with the previous generation Bristol Ridge which remains an OEM-only product for now. We’ve gone into detail about how AM4 will operate, using a split IO design between the CPU and the chipset such that for minimal function, a chipset is not needed, however AMD has pointed out that with Ryzen, AM4 with the right chipset will support USB 3.1 Gen 2 (10 Gbps), NVMe SSDs, SATA-Express, and offer ‘ultimate upgradability’. The latter point may give an indication to the Ryzen based chipsets might offer numerous PCIe lanes, similar to what Intel does on the 100-series. That said, Intel has been developing that feature over years, and the Bristol Ridge chipsets for AM4 that have been announced already are not quite up to par with that, so it will be interesting to see.

We’re still waiting for detailed information on PCIe lane counts on Ryzen, how big that micro-op cache is in the core, if the L3 victim cache has limitations, how good the DDR4 controller is, power consumption, and what exactly the single core performance / IPC level is. Actually AMD did go into more detail with a few of these areas as well.

Power, Performance and Pre-Fetch: AMD SenseMI

Part of the demo in the pre-brief was a Handbrake video transcode, a multithreaded test, showing a near-identical completion time between a high-frequency Ryzen without turbo compared to an i7-6900K at similar frequencies. This mirrors the Blender test we saw back in August, although using a new benchmark this time but still multi-threaded. AMD also fired up some power meters, showing that Ryzen power consumption in this test was a few watts lower than the Intel part, implying that AMD is meeting its targets for power, performance and as a result, efficiency. The 40%+ improvement in IPC/efficiency is still being thrown around, and AMD seems confident that this target has been surpassed.

To that extent, at the pre-briefing, Ryan was shown two systems running Titan X graphics cards in SLI and Battlefield 1 at 4K settings - one system was running Ryzen, and the other an i7-6900K (the 8-core Broadwell-E chip). Ryan was unable to determine an obvious visual difference between the two frame-rate wise, which was the point of the demo.

Mark Papermaster, CTO of AMD, explained during our briefing that during the Zen design stages, up to 300 engineers were working on the core engine with an aggressive mantra of higher IPC for no power gain. This is not an uncommon strategy for core designs. Part of this will be down to two new power modes, that adjust and extend the power/frequency curve, which are part of AMD’s new 5-stage ‘SenseMI’ technology.

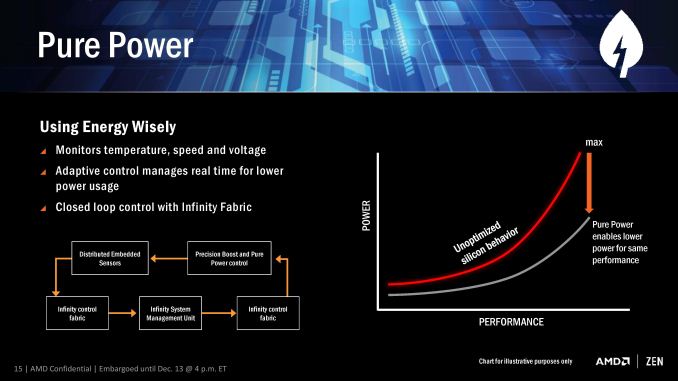

SenseMI Stage 1: Pure Power

A number of recent microprocessor launches have revolved around silicon-optimized power profiles. We are now removed from the ‘one DVFS curve fits all’ application for high-end silicon, and AMD’s solution in Ryzen will be called Pure Power. The short explanation is that using distributed embedded sensors in the design (first introduced in bulk with Carrizo) that monitor temperature, speed and voltage, and the control center can manage the power consumption in real time. The glue behind this technology comes in form of AMD’s new ‘Infinity Fabric’.

‘What is this new Infinity Fabric?’ I hear you say. It was only explained in the context of that it provides control and through the Infinity System Management Unit it can adjust power consumption while keeping in mind everything else that’s happening. The fact that it’s described as a fabric suggests that it goes through the entire processor, connecting various parts together as part of that control. Whether this is something wildly different to what we saw in Carrizo, aside from being the next-gen power adjustment and under a new name, is hard to determine at this point but we are probing for more details.

The upshot of Pure Power is that the DVFS curve is lower and more optimized for a given piece of silicon than a generic DVFS curve, which results in giving lower power at various/all levels of performance. This in turn benefits the next part of SenseMI, Precision Boost.

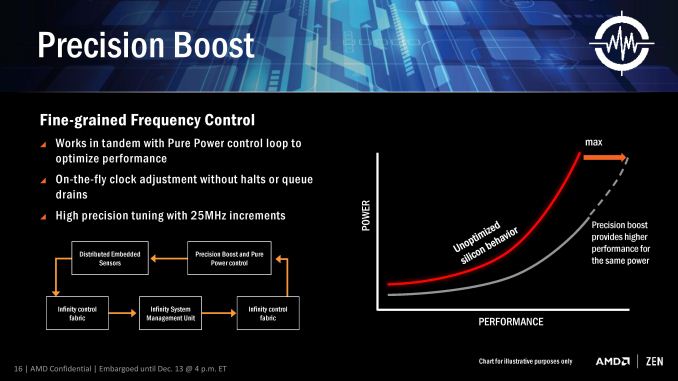

SenseMi Stage 2: Precision Boost

For almost a decade now, most commercial PC processors have invoked some form of boost technology to enable processors to use less power when idle and fully take advantage of the power budget when only a few elements of the core design is needed. We see processors that sit at 2.2 GHz that boost to 2.7 GHz when only one thread is needed, for example, because the whole chip still remains under the power limit. AMD is implementing Precision Boost for Ryzen, increasing the DVFS curve to better performance due to Pure Power, but also offering frequency jumps in 25 MHz steps which is new.

Precision Boost relies on the same Infinity Control Fabric that Pure Power does, but allows for adjustments of core frequency based on performance requirements and suitability/power given the rest of the core. The fact that it offers 25 MHz steps is surprising, however.

Current turbo control systems, on both AMD and Intel, are invoked by adjusting the CPU frequency multiplier. With the 100 MHz base clock on all modern CPUs, one step in frequency multiplier gives 100 MHz jump for the turbo modes, and any multiple of the multiplier can be used on the basis of whole numbers only.

With AMD moving to 25 MHz jumps in their turbo, this means either:

- The base frequency has reduced down to 25 MHz and AMD is able to implement a 136x multiplier to reach 3.4 GHz, or

- AMD can implement fractional multipliers, similar to how processors in the early 2000s were able to negotiate 0.5x multiplier jumps, or

- Precision Boost only applies to internal clocks that the user doesn’t see or control, but can assist with performance.

Without additional information, the second point in that list seems more in line with what would be possible. If we consider that Zen’s original chief designer was Jim Keller (and his team), known for a number of older generation of AMD processors, a similar technology might be in play here. If/when we get more information on it, we will let you know.

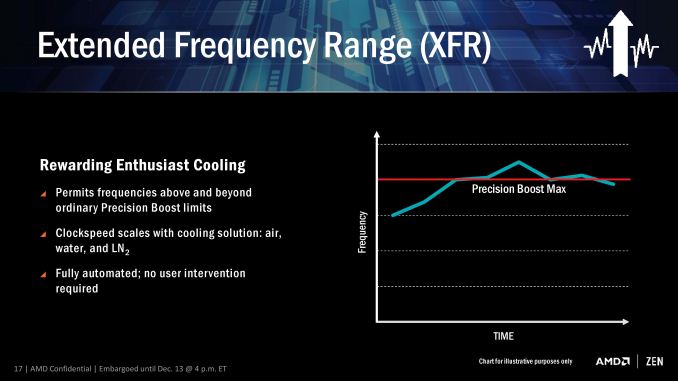

SenseMi Stage 3: Extended Frequency Range (XFR)

The main marketing points of on-the-fly frequency adjustment are typically down to low idle power and higher performance when needed. The current processors on the market have rated speeds on the box which are fixed frequency settings that can be chosen by the processor/OS depending on what level of performance is possible/required. AMD’s new XFR mode seems to do away with this, offering what sounds like an unlimited bound on performance.

The concept here is that, beyond the rated turbo mode, if there is sufficient cooling then the CPU will continue to increase the clock speed and voltage until a cooling limit is reached. This is somewhat murky territory, though AMD claims that a multitude of different environments can be catered for the feature. AMD was not clear if this limit is determined by power consumption, temperature, or if they can protect from issues such as a bad frequency/voltage setting.

By the sounds of it, this is a dynamic adjustment rather than just another embedded look-up table such as P-states. AMD states that XFR is a fully automated system with no user intervention, although I suspect it will still have an on/off switch in the BIOS. It also somewhat negates overclocking if your cooling can support it, which then brings up the issue for overclocking in general: casual users may not ever need to step into the overclocking world if the CPU does it all automatically.

I imagine that a manual overclock will still be king, especially for extreme overclockers competing with liquid nitrogen, as being able to personally fine tune a system might be better than letting the system do it itself. It can especially be true in those circumstances, as sensors on hardware can fail, report the wrong temperature, or may only be calibrated within a certain range.

It does raise the question as to how overclockable Ryzen will be, how many SKUs will be unlocked, or if XFR may only be on certain processors. As the Zen microarchitecture is destined for server and mobile as well, XFR will have different connotations for both of those markets (some of which might not be welcome).

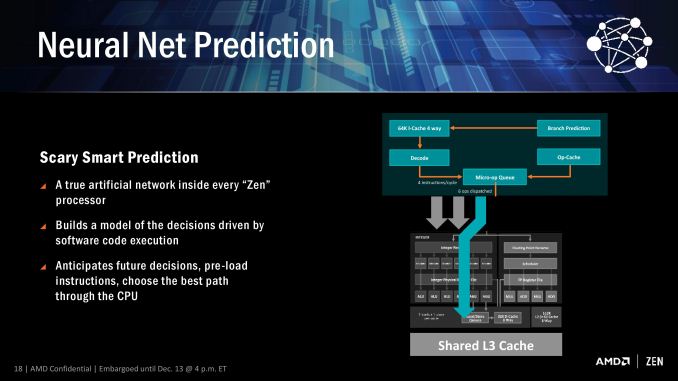

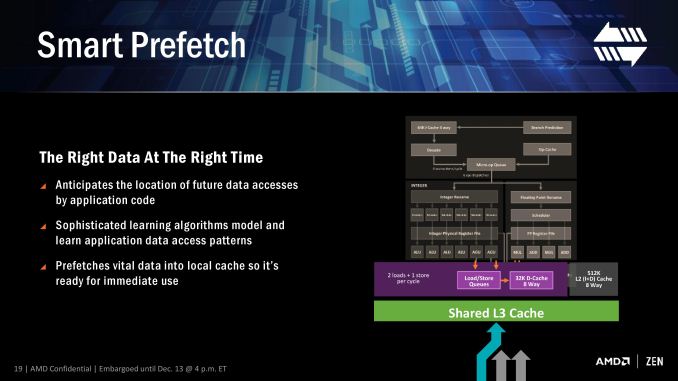

SenseMi Stage 4+5: Neural Net Prediction and Smart Prefetch

Every generation of CPUs from the big companies come with promises of better prediction and better pre-fetch models. These are both important to hide latency within a core which might be created by instruction decode, queuing, or more usually, moving data between caches and main memory to be ready for the instructions. With Ryzen, AMD is introducing its new Neural Net Prediction hardware model along with Smart Pre-Fetch.

AMD is announcing this as a ‘true artificial network inside every Zen processor that builds a model of decisions based on software execution’. This can mean one of several things, ranging from actual physical modelling of instruction workflow to identify critical paths to be accelerated (unlikely) or statistical analysis of what is coming through the engine and attempting to work during downtime that might accelerate future instructions (such as inserting an instruction to decode into an idle decoder in preparation for when it actually comes through, therefore ends up using the micro-op cache and making it quicker).

Modern processors already do decent jobs when repetitive work is being used, such as identifying when every 4th element in a memory array is being accessed, and can pull that data in earlier to be ready in case it is used. The danger of smart predictors however is being overly aggressive – pulling in too much data that old data might be ditched because it’s never used (over prediction), pulling in too much data such that it’s already evicted by the time the data is needed (aggressive prediction), or simply wasting excess power with bad predictions (stupid prediction…).

AMD is stating that Zen implements algorithm learning models for both instruction prediction and prefetch, which will no doubt be interesting to see if they have found the right balance of prefetch aggression and extra work in prediction.

It is worth noting here that AMD will likely draw upon the increased L3 bandwidth in the new core as a key element to assisting the prefetch, especially as the shared L3 cache is a victim cache and designed to contain data already used/evicted to be used again at a later date.

More Details

AMD did confirm that the launch for Ryzen is still Q1, and Naples (the server counterpart for the Zen microarchitecture) is still on for Q2.

Today, AMD is putting on a Livestream called ‘New Horizon’, where all this information is being formally released. I’m at the event live, hopefully running a live blog, and I will try to get some extra time with an engineer that walks by and wants to chat. I want to get more information on the Infinity Fabric, the Neural Net Predictor and chipset integration.

170 Comments

View All Comments

bigboxes - Tuesday, December 13, 2016 - link

Still lacking a lot of details. It would be nice if this was competitive with the i7-6900K, albeit at a lower price point. Wonder why AMD didn't stick with Zen instead of Ryzen. I think Zen had a better name for marketing, if AMD would ever do such a thing.bananaforscale - Tuesday, December 13, 2016 - link

Based on the rendering demos it's as fast if not faster, at a lower TDP.Meteor2 - Tuesday, December 13, 2016 - link

95W, to be precise, for 8 cores 16 threads and 'at least' 3.4 GHz.Meteor2 - Tuesday, December 13, 2016 - link

...while the i7-6900K is 140W.Sttm - Tuesday, December 13, 2016 - link

As a 6900K owner I am not sure that I care about the wattage. This is a part for my home PC, not servers. Performance, and the cost of that performance, is where Zen needs to shine to compete with the 6900k, or lets be realistic the 7900k. Which so far looks good.I hope they manage to beat the 6900k and do so at a price that is about say $600. Put their high end Ryzen up against Intel's mainstream -E offering.

Railander - Tuesday, December 13, 2016 - link

While TDP does relate to power consumption, it is not a unit of power consumption but rather of power dissipation as heat.Having a lower TDP directly affects what sort of cooling solution you need, which obviously translates to smaller/quieter coolers and how much you can push the chip while overclocking.

Tewt - Tuesday, December 13, 2016 - link

I'm sure they mentioned it because anytime AMD gets close in performance, some fan of the competition always throws in a "BUT they have higher TDP so it is not as good a product because I have to spend more on cooling, blah blah blah."bill4 - Thursday, December 15, 2016 - link

oh lord...in rx 480 vs 1060 ti debates i had on reddit, you wouldn't BELIEVE the amount of people who would act like the 1060's slightly lower power draw (efficiency!) was the end all be all! Just funny to see the arguments reversed here.People would hold their nose and exaggerate "oh, the 1060 Ti is 500% more efficient than the 480, what is wrong with AMD!" I'd be like no, it's a few watts, who cares? And what matters (within reason, you dont want a space heater like the FX 9590 chips) is price and performance!

I mean literally people would act like "efficiency" was FAR more important than raw power or price. Just because Nvida happened to have a current, small, advantage there!

Nvidia/Intel fanboys are funny...

inmytaxi - Friday, January 6, 2017 - link

As are the people who are engaging them for some strange reason.bigboxes - Tuesday, December 13, 2016 - link

I run my file server 24/7. I run my HTPC (i7 920) 24/7. I run my main rig (i7 4790K oc)... drumrolll... 24/7. I am not concerned about the cost of running my computers, but less is always better. Less heat, less noise, higher threshold for oc. If the TDP is 95W, while the chip it is being compared to is 140W, that is a huge Δ.